Low Cost Launch- -on on- -Shift Shift Low Cost Launch Delay - PowerPoint PPT Presentation

Low Cost Launch- -on on- -Shift Shift Low Cost Launch Delay Test with Slow Scan Delay Test with Slow Scan Enable (ETS06) Enable (ETS06) Gefu Xu Xu Gefu Adit D. Singh D. Singh Adit Auburn University Auburn University Outline

Low Cost Launch- -on on- -Shift Shift Low Cost Launch Delay Test with Slow Scan Delay Test with Slow Scan Enable (ETS06) Enable (ETS06) Gefu Xu Xu Gefu Adit D. Singh D. Singh Adit Auburn University Auburn University

Outline Outline � Transition Delay Test (Launch Transition Delay Test (Launch- -on on- -Shift, Launch Shift, Launch- -on on- - � Capture) Capture) � The issue of LOS: requiring fast scan enable signals The issue of LOS: requiring fast scan enable signals � � Current approach I: Pipeline structure methods Current approach I: Pipeline structure methods � � Current approach II: Partial Current approach II: Partial- -shift shift- -partial partial- -capture capture � methods methods � Other approaches: Hybrid method and Enhanced Scan Other approaches: Hybrid method and Enhanced Scan � method method � Our solution: Using Delay Test Scan Flip Our solution: Using Delay Test Scan Flip- -flops with slow flops with slow � scan enable signals scan enable signals

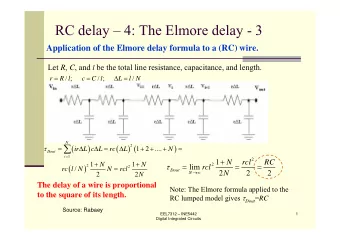

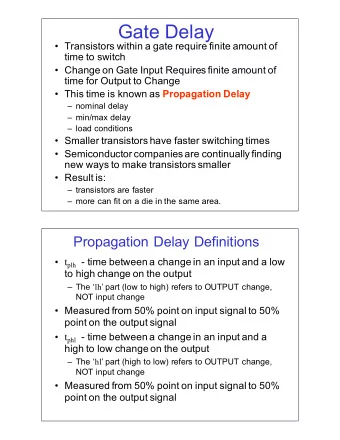

Transition Delay Test Transition Delay Test Delay Test Functional Structure Test Test Speed Path Delay Transition Delay Binning Test Test Launch-On-Shift Launch-On-Capture LOS LOC Figure 1: Classification of Delay Test

LOS & LOC Delay Test LOS & LOC Delay Test Figure 3: Multiplexer based scan flip-flop Figure 2: Overview of scan based delay testing Figure 4: Waveforms for LOS and LOC delay test

LOS & LOC Delay Test LOS & LOC Delay Test Launch-on-Shift (LOS) Launch-on-Capture (LOC) 1)High fault coverage 1) No requirement for fast Advantage 2)Few test patterns scan enable signals 3)Combination ATPG 1) Requiring fast scan 1)Medium fault coverage Disadvantage enable signals 2) More test patterns 3)Sequential ATPG Table1: Comparison of LOS & LOC

Issue of LOS: Requiring Fast Scan Issue of LOS: Requiring Fast Scan Enable Signals Enable Signals � DFT design cost DFT design cost � High speed global scan enable signal - High speed global scan enable signal -> routing the > routing the scan enable signal as clock signal - -> DFT design cost is > DFT design cost is scan enable signal as clock signal expensive expensive � Hard to meet time closure Hard to meet time closure � “From our experience, the design effort involved in From our experience, the design effort involved in “ designing a fast SEN signal and the resulting impact on designing a fast SEN signal and the resulting impact on turnaround time is considered unacceptable for many turnaround time is considered unacceptable for many designs. We believe that this concern is shared by others designs. We believe that this concern is shared by others in the design and test community.” ” (ref.[8]) (ref.[8]) in the design and test community.

Approach I: Pipeline structure Approach I: Pipeline structure methods methods Figure5: Test architecture Figure 6: Last transition generator (LTG) cell

100 1000[10]1110 1 � The values in LTG cell The values in LTG cell � 0 0 determine the test determine the test mode (LOS or LOC). mode (LOS or LOC). � Both LOS and LOC test Both LOS and LOC test � are allowed. are allowed. � Local fast scan enable Local fast scan enable � signals are needed and signals are needed and drivability requirements drivability requirements for these signals are for these signals are considerable. considerable. � Timing critical signals Timing critical signals � (enable signals) (enable signals) complicate layout and complicate layout and timing closure. timing closure. Figure 7: Operation of LTG cell, (b) LOS and (c) LOC

Approach II: Partial- -shift shift- -partial partial- - Approach II: Partial capture methods capture methods Figure 8: Modified Local scan enable Figure 9: Test Structure generator (LSEG) cell

� The value in LSEG The value in LSEG � determines the mode determines the mode (LOC or enhanced (LOC or enhanced LOC). LOC). � LOC and enhanced LOC and enhanced � LOC mode which LOC mode which restricts a subset of restricts a subset of scan chain only scan chain only operating in shift mode operating in shift mode are allowed. are allowed. � Fault coverage is only Fault coverage is only � a little higher than a little higher than pure LOC pure LOC � Timing critical signals Timing critical signals � (enable signals) (enable signals) complicate layout and complicate layout and timing closure. timing closure. Figure 10: Operation of LSEG cell (a) Scan chain (b) Conventional LOC and (c) Enhanced LOC

Other approaches: Hybrid method Other approaches: Hybrid method Figure 11: Fast Scan Enable Signal Generator � Using a slow scan enable signal to generate a Using a slow scan enable signal to generate a � fast scan enable signal fast scan enable signal � Some Scan Flip Some Scan Flip- -flops are controlled by Slow flops are controlled by Slow � Scan Enable signal and other Scan Flip- -flops flops Scan Enable signal and other Scan Flip (few) are controlled by Fast Scan Enable signal. (few) are controlled by Fast Scan Enable signal.

Other approaches: Enhanced Scan Other approaches: Enhanced Scan method method Figure 12: Dual Flip-flop Table 2: Dual Flip-flop operation � Double all scan Flip Double all scan Flip- -flops to allow LOS and LOC flops to allow LOS and LOC � � If partial scan Flip If partial scan Flip- -flops are doubled, it works as flops are doubled, it works as � Partial- -shift shift- -partial partial- -capture mode capture mode Partial

Contribution of this paper Contribution of this paper � Designed a new structure Designed a new structure -- -- Delay Test Delay Test � Scan Flip- -flop (DTSFF) to support LOS flop (DTSFF) to support LOS Scan Flip transition delay testing transition delay testing � Designed modified DTSFF (type I) to Designed modified DTSFF (type I) to � support both LOS and LOC delay testing support both LOS and LOC delay testing � Designed modified DTSFF (type II) to Designed modified DTSFF (type II) to � support mixed LOS and LOC delay testing support mixed LOS and LOC delay testing (even higher fault coverage) (even higher fault coverage)

Experiment results Experiment results 100 95 90 85 80 Fault Coverage 75 70 65 60 55 50 e n 6 8 3 8 4 8 4 7 0 8 8 4 9 2 6 0 0 4 0 6 1 3 0 2 3 g 0 9 4 4 8 8 0 2 4 1 2 6 4 1 2 3 5 9 3 2 8 9 7 3 0 5 2 1 2 4 4 4 3 2 a 2 2 3 3 3 3 4 4 4 5 5 6 7 8 8 9 2 8 5 1 1 1 1 1 5 9 3 5 r S S S S S S S S S S S S S S S S e S S S S S S S S 1 1 v S S A LOC (100k) LOS (100k) ISCAS89 LOS+LOC (200k) MIX (200k)

Conclusion Conclusion � Basic DTSFF allows LOS test with slow scan Basic DTSFF allows LOS test with slow scan � enable signal enable signal � Modified DTSFF (type I & II) allow LOS+ LOC Modified DTSFF (type I & II) allow LOS+ LOC � test and Mix LOS/LOC test test and Mix LOS/LOC test � The overhead for DTSFF is small. The overhead for DTSFF is small. � � The Fault coverage for DTSFF design is high. The Fault coverage for DTSFF design is high. � � DTSFF is compatible with current EDA tools and DTSFF is compatible with current EDA tools and � design flows. design flows.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.