Delay Test Virendra Singh Associate Professor C omputer A - PowerPoint PPT Presentation

Delay Test Virendra Singh Associate Professor C omputer A rchitecture and D ependable S ystems L ab Department of Electrical Engineering Indian Institute of Technology Bombay http://www.ee.iitb.ac.in/~viren/ E-mail: viren@ee.iitb.ac.in

Delay Test Virendra Singh Associate Professor C omputer A rchitecture and D ependable S ystems L ab Department of Electrical Engineering Indian Institute of Technology Bombay http://www.ee.iitb.ac.in/~viren/ E-mail: viren@ee.iitb.ac.in EE-709: Testing & Verification of VLSI Circuits Lecture 28 (28 March 2013) CADSL

Path Delay Fault Cheng’s classification Robustly testable Non-robustly (NR) testable Functional sensitizable (FS) testable Functionally unsensitizable (functionally redundant ) CADSL 28 Mar 2013 EE-709@IITB 2

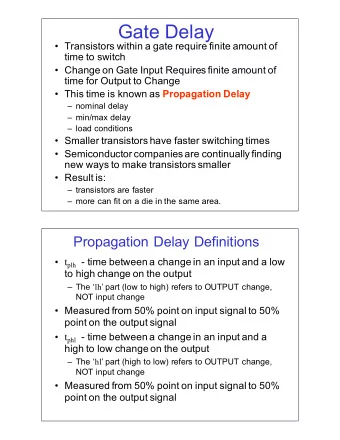

Path Delay Fault Robust testable : detect target PDF independent of delays in rest of the circuit. It must satisfies the following conditions It launches the desired transition at primary input All side inputs of target path settle to non- controlling values under V 2 Whenever the logic transition at an on-input is from non-controlling to controlling value (ncv to cv), each side-input should maintain CADSL 28 Mar 2013 EE-709@IITB 3 steady non-controlling value (ncv)

Path Delay Fault Robust testable CADSL 28 Mar 2013 EE-709@IITB 4

Path Delay Fault Non-Robust (NR ) testable : It must satisfies the following conditions It launches the desired transition at primary input All side-inputs of target path settle to non- controlling values (ncv) under V 2 CADSL 28 Mar 2013 EE-709@IITB 5

Path Delay Fault Functional Sensitizable (FS) testable: Detection of faults on paths that are sensitizable under FS criterion depends on the delays on signals outside the target path It must satisfies the following conditions It launches the desired transition at primary input Whenever the logic transition at an on-input is non-controlling value (ncv) under vector V 2 , each side-input should have non- controlling value (ncv) under V 2 CADSL 28 Mar 2013 EE-709@IITB 6

Path Delay Fault CADSL 28 Mar 2013 EE-709@IITB 7

Path Delay Fault Functionally unsensitizable CADSL 28 Mar 2013 EE-709@IITB 8

Path Delay Fault On-input Side-inputs Testability cv -> ncv Stable cv Untestable Stable ncv Robust cv -> ncv ncv -> cv Untestable ncv -> cv Stable cv Untestable Stable ncv Robust cv -> ncv NR ncv -> cv FS CADSL 28 Mar 2013 EE-709@IITB 9

Robust Test Conditions Real events on target path. Controlling events via target path. V1 V2 V1 V2 V1 V2 V1 V2 U0 U1 U0 U1 U0/F0 U0/F0 U1/R1 U1/R1 V1 V2 V1 V2 S1 S0 S0 S1 U0/F0 U1/R1 U0/F0 U1/R1 CADSL 28 Mar 2013 EE-709@IITB 10

A Five-Valued Algebra Signal States: S0, U0 (F0), S1, U1 (R1), XX. On-path signals: F0 and R1. Off-path signals: F0=U0 and R1=U1 . Input 1 Input 1 S0 U0 S1 U1 XX S0 U0 S1 U1 XX AND OR S0 S0 S0 S0 S0 S0 S0 S0 U0 S1 U1 XX U0 S0 U0 U0 U0 U0 U0 U0 U0 S1 U1 XX Input 2 Input 2 S1 S0 U0 S1 U1 XX S1 S1 S1 S1 S1 S1 U1 S0 U0 U1 U1 XX U1 U1 U1 S1 U1 U1 XX S0 U0 XX XX XX XX XX XX S1 U1 XX Input S0 U0 S1 U1 XX Ref.: NOT Lin-Reddy S1 U1 S0 U0 XX IEEETCAD -87 CADSL 28 Mar 2013 EE-709@IITB 11

Robust Test Generation Test for P3 – falling transition through path P3: Steps A through E E. Set input of AND gate to S0 to justify S0 at output XX S0 S0 U0 D. Change off-path input C. F0 interpreted as U0; to S0 to Propagate R1 propagates through U0 through OR gate AND gate R1 A. Place F0 at path origin Path P3 F0 XX F0 R1 Robust Test: U0 S0, F0, U0 B. Propagate F0 through OR gate; also propagates as R1 through NOT gate CADSL 28 Mar 2013 EE-709@IITB 12

Non-Robust Test Generation Fault P2 – rising transition through path P2 has no robust test. C. Set input of AND gate to propagate R1 to output D. R1 non-robustly propagates XX U1 through OR gate since off- path input is not S0 R1 R1 Path P2 U1 A. Place R1 at path origin R1 R1 U1 U0 Non-robust test requires Static sensitization: XX S0=U0, S1=U1 U0 B. Propagate R1 through OR gate; Non-robust test: interpreted as U1 on off-path signal; U1, R1, U0 propagates as U0 through NOT gate CADSL 28 Mar 2013 EE-709@IITB 13

Functional Sensitizable TG CADSL 28 Mar 2013 EE-709@IITB 14

FS Untestable Faults Fault P2 – falling transition through path P2 has no test. D. F0 cannot be propagated C. Set input of AND gate to through OR gate since off- propagate F0 to output path input is not S0 XX S1 F0 F0 Path P2 S1 A. Place R1 at path origin F0 F0 U0 U1 NO TEST XX U0 B. Propagate R1 through OR gate; Non-robust test: interpreted as U1 on off-path signal; U1, R1, U0 propagates as U0 through NOT gate CADSL 28 Mar 2013 EE-709@IITB 15

Slow-Clock Test Combinational Output Input latches circuit latches Input Output Rated Test test clock test clock clock clock period period Input test clock Output test clock V2 V1 Output applied applied latched CADSL 28 Mar 2013 EE-709@IITB 16

Enhanced-Scan Test CK period PI Combinational PO CK circuit CK TC SCAN- HOLD HL SFF OUT Scanout result V1 settles HL SFF SCANIN Normal Normal HOLD mode mode Scan mode TC CK TC CK: system clock Scanin Scanin TC: test control V1 Result V2 states HOLD: hold signal states latched SFF: scan flip-flop V1 PI V2 PI HL: hold latch applied applied CADSL 28 Mar 2013 EE-709@IITB 17

Normal-Scan Test V2 states generated, (A) by one-bit scan shift of V1, or Result (B) by V1 applied in functional mode. latched V2 PIs V1 PIs PI Combinational PO applied applied Result Scanin Path Gen. V2 circuit tested scanout V1 states states t CK TC SCAN- OUT Slow clock Rated SFF CK period TC Normal mode Scan mode Scan mode SFF (A) SCANIN Slow CK CK TC period TC CK: system clock Scan mode Normal mode Scan mode (B) TC: test control SFF: scan flip-flop CADSL 28 Mar 2013 EE-709@IITB 18

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.