Clocking & Timing Asynchronous Self Timed Design Self Timed - PowerPoint PPT Presentation

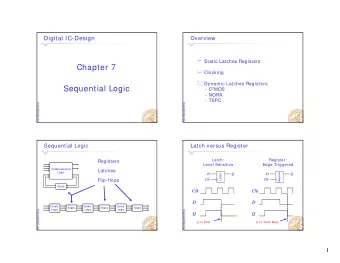

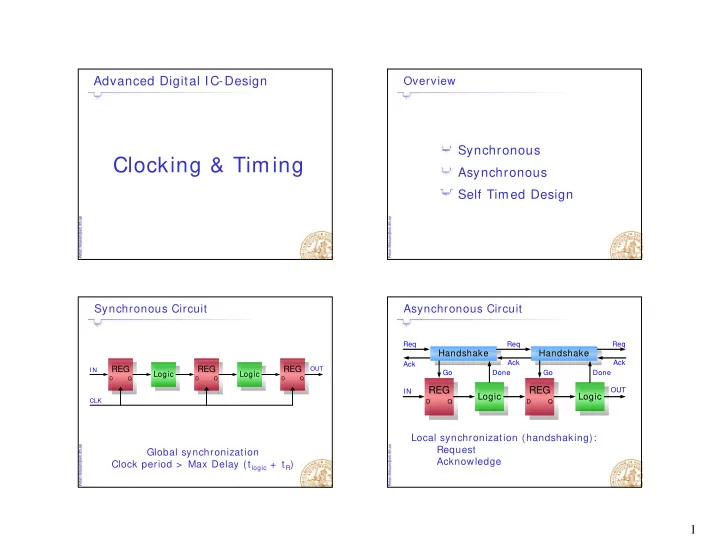

Advanced Digital IC-Design Overview Synchronous Clocking & Timing Asynchronous Self Timed Design Self Timed Design Synchronous Circuit Asynchronous Circuit Req Req Req Handshake Handshake A k Ack Ack A k Ack REG REG REG OUT

Advanced Digital IC-Design Overview Synchronous Clocking & Timing Asynchronous Self Timed Design Self Timed Design Synchronous Circuit Asynchronous Circuit Req Req Req Handshake Handshake A k Ack Ack A k Ack REG REG REG OUT IN Go Done Go Done Logic Logic D Q D Q D Q REG REG OUT IN Logic Logic CLK D Q D Q Local synchronization (handshaking): Request Global synchronization Acknowledge Clock period > Max Delay (t logic + t R ) 1

Globally Async Locally Sync (GALS) Synchronous Design The purpose of the clock is to The purpose of the clock is to Clocked Domain Clocked Domain Interface Interface REG REG Synchronize the registers on the chip with IN OUT Logic each other D Q D Q Req Req Ack Ack Synchronize the registers on the chip with the external world Local Local Clock Clock skew is a large problem Asynchronous Environment Sequential Logic Latch versus Register Latch stores data when clock is low (high) Registers Flip-Flop (or Register) stores data when clock rises (falls) Combinational Latches Latches Latch: Logic Register: Level Sensitive Edge Triggered Flip-flops Register D Q D Q Latch State Clk Clk Clk Clk Comb. Comb. Comb. State State State D D Logic Logic Logic Q Q Q on Data Q on Clock Edge 2

Clock Non-Idealities Clock Non-Idealities Both skew and jitter affects the cycle time Clock skew Skew might lead to race through the registers Spatial a iation in tempo all eq i alent Spatial variation in temporally equivalent clock edges Clock jitter Same clock Temporal variations in consecutive edges of at two the clock signal the clock signal different locations on the chip t skew t jitter Clock Non-Idealities - Feedthrough Example – Clock System V DD (Always on) V DD Global Φ Clock feedthrough Module 1 Clock 2,5 N = × f f Q SYS CLK A M Enable 2 System f Data Clock CLK Phase 1,5 Module 2 De- Locked B skew Φ Loop Q Local 0,5 Clock C Signals Enable 3 N N M Φ Module 3 -0,5 0 0,5 1 Time, ns Clock feedthrough On-Chip Clock Clock Clocked Coupling in dynamic devices Generation Gating Modules can lift the output 3

Synchronous Pipelined Datapath Clock Skew Absolute Skew Relative Skew 10x10 mm Chip Example: 15 mm wire R 1 R 2 R 3 R 4 In Logic Logic Logic D Q D Q D Q D Q C = 300 fF Block # 1 Block # 2 Block # 3 R = 4 k Ω t pd,reg t pd 1 t pd 2 t pd 3 CLK Delay Delay Delay t pHL = 0.69 RC = 0.8 ns “Max frequency” The delay give CLK clock skew 1 1 = = 600 MHz × 2 t 2 0.8 ns pHL Δ L = 15mm Clock Skew Setup- and Hold-times Negative Skew Data bus REG REG REG Abs Log Clock line Out REG In t jitter t setup t jitter t hold R jitter setup jitter hold CLK Positive Skew Clock and data routing 4

Clock Skew General Clock Distribution Tree φ 1 Branches Ext. CLK CLK Leaves Root R t Trunk Clock φ 2 Source φ 1 φ 1 φ 2 Have a large relative skew Large skew require large non-overlap Balanced Clock Net Clock Distribution: H-Tree Distributed Buffers Small relative skew All wires and buffers are Absolute skew of carefully balanced less importance less importance Clock Clock 5

Clock Distribution: H-Tree IBM G4 Processor A balanced H- tree structure Realistic Achieves a skew control of H-Tree ± 25 ps Symmetric Clock Distribution Networks Distributed Buffers Small relative skew Absolute skew of less importance less importance H-tree X-tree Clock 6

Clock Grid Clock Deskewing Clock Low impedance interconnect Delay Line Delay Line Deskew Control Ph Phase Clock Det. Power Hungry Clock Ring Example: Alpha 21164 (0.55um) Clock Frequency 300MHz Clock Transistors 10 Million AVG AVG AVG AVG AVG AVG Total Clock Load 3.75nF AVG AVG Local Clock Power 20W (out of 50W) Clock Levels 2 Clocks AVG AVG Driver Size Driver Size 58cm 58cm A A Clock Grid AVG AVG AVG TSPC 7

Example: Alpha 21164 Example: Alpha 21164 Clock Drivers 600 MHz Alpha “Hybrid” 600 MHz Alpha Relative Skew 72ps Four clock grids under a balanced Clock clock net 8

Skew Analysis - Example Skew Analysis - Example L L L a. Determine the L M M R 1 R 2 L L L R 3 R 1 R 2 L L L R 3 U U minimum clock L X L X period time if clock clk lk clk lk skew is disregarded Positive "clock skew" Positive "clock skew" a. Determine the minimum clock period time if clock skew is disregarded. R 1 to R 2 , t R + 2t L + t m + t S = 0.5+ 2* 3.0+ 1.0+ 0.5 = 8ns b. Determine the minimum clock period time if there is 1ns positive clock skew between adjacent registers. R 2 to R 3 , t R + 3t L + t S = 0.5+ 3* 3.0+ 0.5 = 10ns c. Determine the minimum clock period time if there is 3ns positive clock skew between R 2 to R 2 , t R + 2t L + t m + t S = 0.5+ 2* 3.0+ 1.0+ 0.5 = 8ns adjacent registers. d. Calculate the maximum “clock skew” for the datapath, both positive and negative if the d. Calculate the maximum clock skew for the datapath, both positive and negative if the Answer: The minimum clock period time is 10 ns Answer: The minimum clock period time is 10 ns clock signal has a period of 16ns. Register R setup time t S 0.5 ns Register R setup time t S 0.5 ns Register R delay time t R 0.5 ns Register R delay time t R 0.5 ns Logic L delay time t L 3.0 ns Logic L delay time t L 3.0 ns Mux delay time t M 1.0 ns Mux delay time t M 1.0 ns Skew Analysis - Example Skew Analysis - Example b. Determine the c. Determine the L L L L minimum clock period minimum clock period M M R 1 R 2 L L L R 3 R 1 R 2 L L L R 3 U U time if there is 1ns time if there is 3ns L X L X positive clock skew positive clock skew clk lk clk lk between adjacent between adjacent Positive "clock skew" Positive "clock skew" registers. registers R 2 to R 3 , t R + 3t L + t S -t SKEW = 0.5+ 3* 3.0+ 0.5-1 = 9ns R 2 to R 2 , t R + 2t L + t m + t S = 0.5+ 2* 3.0+ 1.0+ 0.5 = 8ns Answer: The minimum clock period time is 9 ns (No skew in feedback) Register R setup time t S 0.5 ns Register R setup time t S 0.5 ns Register R delay time t R 0.5 ns Register R delay time t R 0.5 ns Logic L delay time t L 3.0 ns Logic L delay time t L 3.0 ns Mux delay time t M 1.0 ns Mux delay time t M 1.0 ns 9

Skew Analysis - Example Synchronizing Signals (Metastability) d. Calculate the L L maximum “clock skew” M From asynchronous domains or R 1 R 2 L L L R 3 U for the datapath, both L X From synchronous domains with different clock positive and negative if clk lk the clock signal has a periods Positive "clock skew" period of 16ns Negative skew - R 2 to R 3 , 16-t R + 3t L + t S = 16-0.5-3* 3.0-0.5 = 6ns (6 ns for clk to R 2 plus 10 ns for signal through logic) Asynchronous Asynchronous synchronous synchronous Positive skew - R 1 to R 2 , t R + t L + t m + t S = 0.5+ 3.0+ 1.0+ 0.5 = 5ns system system system system system system t (R 2 must close before signal arrives) Register R setup time t S 0.5 ns Register R delay time t R 0.5 ns synchronization synchronization Logic L delay time t L 3.0 ns Mux delay time t M 1.0 ns Synchronizing Signals (Metastability) Synchronizing Signals (Metastability) Can occur if the setup t SU , hold time t H , or clock Metastable state: possible output from a flip-flop pulse width t PW of a flip-flop is not met DATA IN D Q Q1 Aperture window CLK t W t res t res is DATA IN t SU important important CLK for MTBF t res “1” t CO Q1 “0” t W = Time window where input transition may cause a metastable condition Many designers are not aware of t SU = Actual clock setup time for flip-flop metastability t CO = Actual flip-flop propagation delay t res = Metastability resolution time 10

× K t Metastability Metastability 2 res × × = K f f MTBF e 1 CLK DATA × MTBF variations due to the metastability K t 2 res resolution time t res × × = = K f f MTBF MTBF e e 1 CLK DATA 11 11 10 1000 years 10 10 9 10 Mean Time Between Failure (MTBF) is 1 year 8 10 exponential 7 10 MTBF 1 month (seconds) t res is the slack time available for settling 6 10 5 10 1 day K 1 and K 2 are constants that are K and K are constants that are ACTEL ACT 1 Devices i 4 10 f DATA = 1 MHz 1 hour characteristics of the flip-flop 3 10 F CLOCK = 10 MHz 2 10 f CLK and f DATA are the frequency of the 1 10 synchronizing clock and asynchronous data 2 4 6 8 10 t res (ns) t res = available slack time (ns) Synchronizer Synchronizer Asynchronous input CLK Timing Violation FF1 FF2 Q 1 Q 1 Q 2 Q 2 D D D Da Ds D D Q D Q Leads to Metastability Q 1 Correct in next CLK register if Q 1 have Synchronized signal Asynchronous input become stable Q 2 FF2 FF1 If D is in the aperture time (setup+ hold) of the flip flop – Global low-skew clock Q 1 Da D Ds Q 2 D Q D Q Q 1 is uncertain However, FF2 might have registered a proper data before CLK CLK Much higher probability for a stable Q 2 than Q 1 A5 Synchronized signal 11

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.