CENG 342 Digital Systems LED Time-multiplexing Larry Pyeatt - PowerPoint PPT Presentation

CENG 342 Digital Systems LED Time-multiplexing Larry Pyeatt SDSM&T 7-segment Display The Nexys A7 board has eight 7-segment LED displays. They share 8 signals specifying which segments to light, and each display has its own anode which

CENG 342 – Digital Systems LED Time-multiplexing Larry Pyeatt SDSM&T

7-segment Display The Nexys A7 board has eight 7-segment LED displays. They share 8 signals specifying which segments to light, and each display has its own anode which controls whether or not its segments are lit. Time-multiplexing is a method where we light each LED, one at a time, in rapid succession. If if the “refresh rate” is high enough, then it appears to the human eye that all of the LEDs are continuously illuminated. Any rate above 60 Hz is adequate, but the higher the rate, the more power is dissipated. We will try for around 95 Hz.

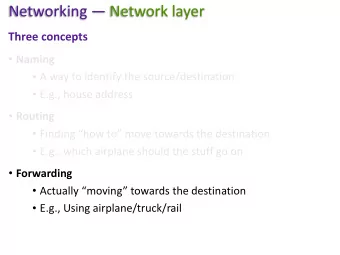

Time Multiplexing Basic idea: 3-bit control signal to control 8-to-1 multiplexing and generate active-low enable signals ( an x ). Can we just use a 3-bit binary counter and feed its outputs into a mux and a decoder? The proper rate is around 100 Hz. The A7 board has a built-in 100 MHz clock. We can use the 100 MHz clock, but how do we reduce a 100 MHz clock to around 100 Hz? A binary counter is a good tool to achieve this goal. How many bits are needed in the binary counter? In the design, 100MHz 100Hz = 1000000. This indicates we need to divide by about one million. How many bits gives us a count of about 1 million? a b c d e f g dp an 7 an 6 an 5 an 4 an 3 an 2 an 1 an 0

Component Schematic 7-Segment Display Controller 5 × 8 Register File Hex to 7-segment Decoder 5 5 Data_In data_in data_out hex_in 8 3 sseg_out sseg Address in_select out_select Write write Enable enable 3 to 8 Decoder Reset reset out 0 an 0 out 1 an 1 select out 2 an 2 out 3 an 3 out 4 an 4 out 5 an 5 Counter out 6 an 6 3 enable out 7 an 7 Reset Clock

Register File Array of 5-bit registers Decoder (with enable) to enable register for writing Mux to select register for output 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 package my_package is type slv_array_5 is array(natural range <>) of std_logic_vector(4 downto 0); 6 type slv_array_8 is array(natural range <>) of std_logic_vector(7 downto 0); 7 type slv_array_16 is array(natural range <>) of std_logic_vector(15 downto 0); 8 9 end package;

Multiplexor 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 use work.my_package.all; 5 6 entity generic_mux_5 is generic(sel_bits:integer:=1); -- number of selector bits 7 port( 8 sel: in std_logic_vector(sel_bits -1 downto 0); -- selector inputs 9 d_in:in slv_array_5(2**sel_bits -1 downto 0); 10 Y: out std_logic_vector(4 downto 0) 11 12 ); 13 end generic_mux_5; 14 15 architecture arch of generic_mux_5 is 16 begin 17 process(sel,d_in) 18 variable sel_n:natural; 19 begin 20 sel_n := to_integer(unsigned(sel)); 21 Y <= d_in(sel_n); 22 end process; 23 end arch;

Decoder 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 entity generic_decoder is 6 generic( 7 bits:integer:=1 -- number of selector inputs 8 ); 9 port( 10 sel: in std_logic_vector(bits-1 downto 0); -- selector inputs 11 Y: out std_logic_vector(2**bits-1 downto 0) 12 ); 13 end generic_decoder; 14 15 architecture arch of generic_decoder is 16 begin process(sel) 17 variable sel_n:natural; 18 begin 19 Y <= (others=>’1’); 20 sel_n := to_integer(unsigned(sel)); 21 Y(sel_n) <= ’0’; 22 end process; 23

Decoder with Enable 29 library ieee; 30 use ieee.std_logic_1164.all; 31 use ieee.numeric_std.all; 32 33 entity generic_decoder_with_enable is generic( bits:integer:=1 ); -- number of selector inputs 34 port( 35 en: in std_logic; 36 sel: in std_logic_vector(bits-1 downto 0); -- selector inputs 37 Y: out std_logic_vector(2**bits-1 downto 0) 38 39 ); 40 end generic_decoder_with_enable; 41 42 architecture arch of generic_decoder_with_enable is 43 begin 44 process(en,sel) 45 variable sel_n:natural; 46 begin 47 if en=’1’ then 48 Y <= (others=>’1’); 49 else Y <= (others=>’1’); 50 sel_n := to_integer(unsigned(sel)); 51 Y(sel_n) <= ’0’; 52 end if; 53 end process; 54 55 end arch;

Register 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 entity generic_register is 6 generic(bits:integer:=4); -- number of bits 7 port( en: in std_logic; -- active low enable 8 clk: in std_logic; -- rising edge-triggered 9 reset:in std_logic; -- active low asynchronous reset 10 d: in std_logic_vector(bits-1 downto 0); q: out std_logic_vector(bits-1 downto 0)); 11 12 end generic_register; 13 14 architecture arch of generic_register is signal latched_data:std_logic_vector(bits-1 downto 0); 15 16 begin process(en,clk,reset) 17 begin 18 if reset = ’0’ then 19 latched_data <= (others => ’0’); 20 else 21 if en=’0’ and clk’event and clk=’1’ then 22 latched_data <= d; 23 end if; 24 end if; 25 end process; 26 q<=latched_data; 27 28 end arch;

Register File – Entity Declaration 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 use work.my_package.all; 5 6 entity generic_register_file_5 is generic(n_sel:integer:=1); -- number of bits for selecting a register 7 port( 8 en: in std_logic; -- active low enable 9 clk: in std_logic; -- rising edge-triggered 10 rst: in std_logic; -- active low asynchronous reset 11 dsel: in std_logic_vector(n_sel-1 downto 0); 12 d: in std_logic_vector(4 downto 0); 13 qsel: in std_logic_vector(n_sel-1 downto 0); 14 q: out std_logic_vector(4 downto 0) 15 ); 16 17 end generic_register_file_5;

Register File – Architecture 19 architecture arch of generic_register_file_5 is signal enable:std_logic_vector(2**n_sel-1 downto 0); 20 signal reg_data:slv_array_5(2**n_sel-1 downto 0); 21 22 begin 23 regs: for i in 0 to 2**n_sel -1 generate 24 reg: entity work.generic_register(arch) 25 generic map(bits=>5) 26 port map(en=>enable(i),clk=>clk,reset=>rst,d=>d,q=>reg_data(i)); 27 end generate regs; 28 29 outmux: entity work.generic_mux_5(arch) 30 generic map(sel_bits=>n_sel) 31 port map(sel=>qsel,d_in=>reg_data,Y=>q); 32 indec: entity work.generic_decoder_with_enable(arch) 33 generic map(bits=>n_sel) 34 port map(en=>en,sel=>dsel,y=>enable); 35 36 37 end arch;

Component Schematic 7-Segment Display Controller 5 × 8 Register File Hex to 7-segment Decoder 5 5 Data_In data_in data_out hex_in 8 3 sseg_out sseg Address in_select out_select Write write Enable enable 3 to 8 Decoder Reset reset out 0 an 0 out 1 an 1 select out 2 an 2 out 3 an 3 out 4 an 4 out 5 an 5 Counter out 6 an 6 3 enable out 7 an 7 Reset Clock

Hex to 7-segment Decoder 1 library ieee; 2 use ieee.std_logic_1164.all; 3 4 entity hex_to_sseg is port( hex: in std_logic_vector(3 downto 0); 5 dp: in std_logic; 6 sseg: out std_logic_vector(7 downto 0)); 7 8 end hex_to_sseg; 9 10 architecture arch of hex_to_sseg is 11 begin 12 with hex select 13 sseg(6 downto 0) <= 14 "1000000" when "0000", "1111001" when "0001", 15 "0100100" when "0010", "0110000" when "0011", 16 "0011001" when "0100", "0010010" when "0101", 17 "0000010" when "0110", "1111000" when "0111", 18 "0000000" when "1000", "0011000" when "1001", 19 "0001000" when "1010", "0000011" when "1011", 20 "1000110" when "1100", "0100001" when "1101", 21 "0000110" when "1110", "0001110" when others; 22 sseg(7) <= not dp; 23 end arch;

Counter 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 entity generic_counter is generic(bits:integer:=4); 6 port( clk: in std_logic; 7 rst: in std_logic; -- asynch reset (active low) 8 q: out std_logic_vector(bits-1 downto 0)); 9 10 end generic_counter; 11 12 architecture arch of generic_counter is signal data:unsigned(bits-1 downto 0); 13 14 begin process(clk,rst) 15 begin 16 if rst = ’0’ then 17 data <= (others => ’0’); 18 else 19 if clk’event and clk = ’1’ then 20 data <= data + 1; 21 end if; 22 end if; 23 end process; 24 25 q <= std_logic_vector(data); 26 27 28 end arch;

Component Schematic 7-Segment Display Controller 5 × 8 Register File Hex to 7-segment Decoder 5 5 Data_In data_in data_out hex_in 8 3 sseg_out sseg Address in_select out_select Write write Enable enable 3 to 8 Decoder Reset reset out 0 an 0 out 1 an 1 select out 2 an 2 out 3 an 3 out 4 an 4 out 5 an 5 Counter out 6 an 6 3 enable out 7 an 7 Reset Clock

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.