CENG 342 Digital Systems Constants and Generics Larry Pyeatt - PowerPoint PPT Presentation

CENG 342 Digital Systems Constants and Generics Larry Pyeatt SDSM&T 4-to-1 Mulitplexer Schematic and Truth Table Boolean function: F = i 0 sel 1 sel 0 + i 1 sel 1 sel 0 + i 2 sel 1 sel 0 + i 3 sel 1 sel 0 Routing circuits Conditional

CENG 342 – Digital Systems Constants and Generics Larry Pyeatt SDSM&T

4-to-1 Mulitplexer Schematic and Truth Table Boolean function: F = i 0 sel 1 sel 0 + i 1 sel 1 sel 0 + i 2 sel 1 sel 0 + i 3 sel 1 sel 0 Routing circuits Conditional signal assignment Selected signal assignment if statement case statement

2-bit Comparator 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 a 1 a 0 b 1 b 0 gt lt eq 5 entity cmp_2bit is 0 0 0 0 0 0 1 port( a : in unsigned(1 downto 0); 6 b : in unsigned(1 downto 0); 7 0 0 0 1 0 1 0 lt,gt,eq : out std_logic); 8 0 0 1 0 0 1 0 9 end cmp_2bit; 0 0 1 1 0 1 0 10 0 1 0 0 1 0 0 11 architecture if_arch of cmp_2bit is 12 begin 0 1 0 1 0 0 1 process(a, b) 13 0 1 1 0 0 1 0 14 begin 0 1 1 1 0 1 0 15 lt <= ’0’; 1 0 0 0 1 0 0 16 gt <= ’0’; 17 eq <= ’0’; 1 0 0 1 1 0 0 18 if a > b then 1 0 1 0 0 0 1 19 gt <= ’1’; 1 0 1 1 0 1 0 20 else 1 1 0 0 1 0 0 21 if a < b then 22 lt <= ’1’; 1 1 0 1 1 0 0 23 else 1 1 1 0 1 0 0 eq <= ’1’; 24 1 1 1 1 0 0 1 end if; 25 end if; 26 end process; 27 28 end if_arch;

Testbench for 2-bit Comparator Use concurrent processes to toggle the input bits. p2: process 25 begin 26 t1(1) <= ’0’; 27 1 library ieee; loop 28 2 use ieee.std_logic_1164.all; wait for 100ns; 29 3 use ieee.numeric_std.all; t1(1) <= not t1(1); 30 4 end loop; 5 entity cmp_2bit_test is 31 end process; 6 end cmp_2bit_test; 32 33 7 p3: process 8 architecture test_arch of cmp_2bit_test is 34 begin signal t0,t1 : unsigned(1 downto 0); 35 9 t0(0) <= ’0’; signal eq,lt,gt : std_logic; 36 10 loop 11 begin 37 wait for 200ns; uut: entity work.cmp_2bit(if_arch) 38 12 t0(0) <= not t0(0); port map(a=>t0, b=>t1, 39 13 end loop; lt=>lt, gt=>gt, eq=>eq); 40 14 end process; 41 15 p1: process 42 16 p4: process begin 43 17 begin t1(0) <= ’0’; 44 18 t0(1) <= ’0’; loop 45 19 46 loop wait for 50ns; 20 47 wait for 400ns; t1(0) <= not t1(0); 21 48 t0(1) <= not t0(1); end loop; 22 49 end loop; end process; 23 50 end process;

Testbench Using Loops 53 architecture loop_test_arch of cmp_2bit_testbench is signal t0,t1 : unsigned(1 downto 0); 54 signal eq,lt,gt : std_logic; 55 56 begin uut: entity work.cmp_2bit(if_arch) 57 port map(a=>t0, b=>t1, lt=>lt, gt=>gt, eq=>eq); 58 59 process1:process 60 variable m, n: integer; 61 begin 62 t0 <= "00"; 63 t1 <= "00"; 64 for n in 0 to 3 loop 65 t1 <= to_unsigned(n,2); 66 for m in 0 to 3 loop 67 t0 <= to_unsigned(m,2); 68 wait for 50 ns; 69 end loop; 70 end loop; 71 end process; 72 73 end loop_test_arch; Many other variations are possible.

Simulation Results

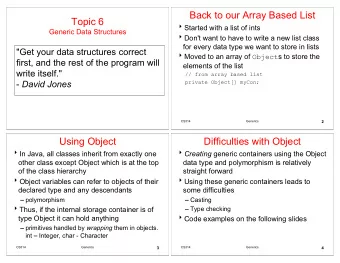

Variables, Signals, Constants, Generics Signals are declared at the start of an architecture , and can be used anywhere within that architecture. Signal declaration: signal list_of_names : type_name[:=initial_value]; Signals must be declared within an architecture and their scope (visibility) is local to that architecture. Variables can be declared at the start of a process . Variable declaration: variable list_of_names : type_name[:=initial_value]; Variables must be declared within a process and their scope (visibility) is local to that process. Constants can be declared at the start of an architecture or processes . Constant declaration: constant constant_name : type_name := value; Their scope is the architecture or process where they are declared. Generics can be used to assign desired values in components in other code (will be described shortly).

Constants Constants can be used in expressions and for specifying array boundaries. Examples: constant DATA_BIT: integer := 4; 1 constant DATA_RANGE: integer :=2**DATA_BIT -1; 2 Constants can not be changed. Example: 4-bit adder with carry-out 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 entity add_w_carry is port( 6 a, b: in std_logic_vector(3 downto 0); 7 sum: out std_logic_vector(4 downto 0); 8 ); 9 10 end add_w_carry;

Constants – continued Basic architecture: 12 architecture hard_arch of add_w_carry is signal a_ext, b_ext, sum_ext: unsigned(4 downto 0); 13 14 begin a_ext <= unsigned(’0’ & a); -- concatenate ’0’ bit to front 15 b_ext <= unsigned(’0’ & b); -- concatenate ’0’ bit to front 16 sum_ext <= a_ext + b_ext; -- perform addition 17 sum <= std_logic_vector(sum_ext(4 downto 0)); -- type conversion 18 19 end hard_arch; Using a constant makes it easier to understand and maintain 21 architecture const_arch of add_w_carry is constant N: integer := 4; -- most significant output bit is 4 22 signal a_ext, b_ext, sum_ext: unsigned(N downto 0); 23 24 begin a_ext <= unsigned(’0’ & a); 25 b_ext <= unsigned(’0’ & b); 26 sum_ext <= a_ext + b_ext; 27 sum <= std_logic_vector(sum_ext(N downto 0)); 28 29 end const_arch;

Generics Generic provides a way to pass information into components at instantiation Can not be modified in the architecture, but can be re-defined in components. Declared inside an entity declaration, just before the port declaration. Syntax: 1 entity entity_name is generic( 2 generic_name: data_type :=value; 3 generic_name: data_type :=value); 4 port( port_declaratons ); 5 6 end entity_name

Generic Declaration Example 1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 entity gen_add_w_carry is generic(N: integer:=4); 6 port(a, b: in std_logic_vector(N-1 downto 0); 7 sum: out std_logic_vector(N downto 0)); 8 9 end gen_add_w_carry; 10 11 architecture arch of gen_add_w_carry is signal a_ext, b_ext, sum_ext: unsigned(N downto 0); 12 13 begin a_ext <= unsigned(’0’ & a); 14 b_ext <= unsigned(’0’ & b); 15 sum_ext <= a_ext + b_ext; 16 sum <= std_logic_vector(sum_ext(N downto 0)); 17 18 end arch;

Generic Mapping When the adder is used as a component in other code, the desired value can be assigned to the generic. This is called generic mapping . Generics allow the programmer to design scaleable code. The width of a circuit can be specified to meet a specific need. A generic decoder can be instantiated as an n by 2 n decoder. A generic mux can be an m -bit 2 n -to-1 mux. Example: signal a4, b4: unsigned (3 downto 0); 1 signal sum5: unsigned (4 downto 0); 2 signal a8, b8: unsigned (7 downto 0); 3 signal sum9: unsigned (8 downto 0); 4 5 ... --instantiate 8-bit adder 6 adder_8_unit: work.gen_add_w_carry (arch) 7 generic map (N=>8) 8 port map(a=>a8, b=>b8, sum=>sum9); 9 --if no generic mapping is given, the default value is used 10 adder_4_unit: work. gen_add_w_carry (arch) 11 port map(a=>a4, b=>b4, sum=>sum5); 12

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.