Basics of Digital Logic Design 0 1 1 0 1 0 0 1 1 1 0 1 0 - PowerPoint PPT Presentation

Signals, Logic Operations and Gates CSE 675.02: Introduction to Computer Rather than referring to voltage levels of signals, we shall consider Architecture signals that are logically 1 or 0 (or asserted or de-asserted). Logic XOR NOT AND

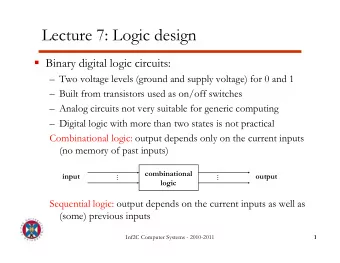

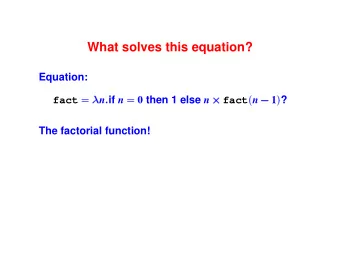

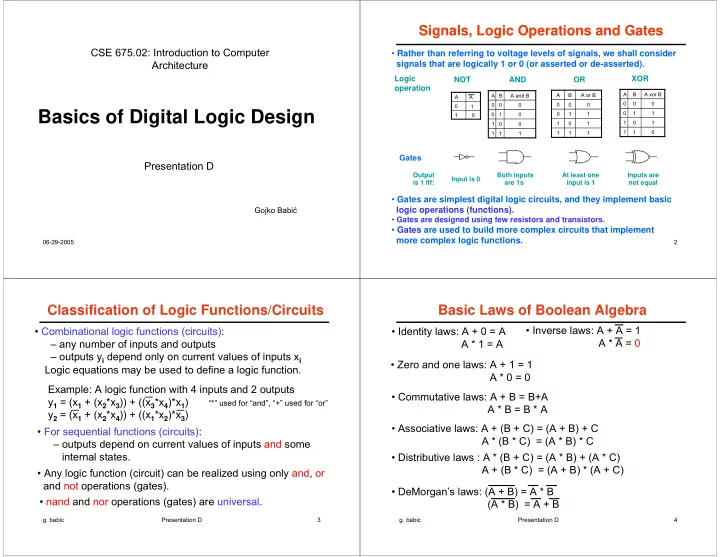

Signals, Logic Operations and Gates CSE 675.02: Introduction to Computer • Rather than referring to voltage levels of signals, we shall consider Architecture signals that are logically 1 or 0 (or asserted or de-asserted). Logic XOR NOT AND OR operation A B A xor B A B A and B A B A or B A A 0 0 0 0 0 0 0 0 0 0 1 Basics of Digital Logic Design 0 1 1 0 1 0 0 1 1 1 0 1 0 1 1 0 1 1 0 0 1 1 1 1 1 0 1 1 1 Gates Presentation D Output Both inputs At least one Inputs are Input is 0 is 1 iff: are 1s input is 1 not equal • Gates are simplest digital logic circuits, and they implement basic Gojko Babi ć logic operations (functions). • Gates are designed using few resistors and transistors. • Gates are used to build more complex circuits that implement more complex logic functions. 06-29-2005 2 Classification of Logic Functions/Circuits Basic Laws of Boolean Algebra • Inverse laws: A + A = 1 • Combinational logic functions (circuits): • Identity laws: A + 0 = A A * A = 0 – any number of inputs and outputs A * 1 = A – outputs y i depend only on current values of inputs x i • Zero and one laws: A + 1 = 1 Logic equations may be used to define a logic function. A * 0 = 0 Example: A logic function with 4 inputs and 2 outputs • Commutative laws: A + B = B+A y 1 = (x 1 + (x 2 *x 3 )) + ((x 3 *x 4 )*x 1 ) “*” used for “and”, “+” used for “or” A * B = B * A y 2 = (x 1 + (x 2 *x 4 )) + ((x 1 *x 2 )*x 3 ) • Associative laws: A + (B + C) = (A + B) + C • For sequential functions (circuits): A * (B * C) = (A * B) * C – outputs depend on current values of inputs and some internal states. • Distributive laws : A * (B + C) = (A * B) + (A * C) A + (B * C) = (A + B) * (A + C) • Any logic function (circuit) can be realized using only and, or and not operations (gates). • DeMorgan’s laws: (A + B) = A * B • nand and nor operations (gates) are universal. (A * B) = A + B g. babic Presentation D 3 g. babic Presentation D 4

Simple Circuit Design: Example Truth Tables • Another way (in addition to logic equations) to define certain Given logic equations, it is easy to design a corresponding circuit functionality y 1 = (x 1 + (x 2 *x 3 )) + ((x 3 *x 4 )*x 1 ) = x 1 + (x 2 *x 3 ) + (x 3 *x 4 *x 1 ) • Problem: their sizes grow exponentially with number of inputs. y 2 = (x 1 + (x 2 *x 4 )) + ((x 1 *x 2 )*x 3 ) = x 1 + (x 2 *x 4 ) + (x 1 *x 2 *x 3 ) inputs outputs x 1 x 2 x 3 y 1 y 2 What are logic equations 0 0 0 0 0 corresponding to this table? 0 0 1 1 0 0 1 0 1 0 y 1 = x 1 + x 2 + x 3 0 1 1 1 0 y 2 = x 1 * x 2 * x 3 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 Design corresponding circuit. 1 1 1 1 1 g. babic Presentation D 5 g. babic Presentation D 6 Programmable Logic Array - PLA Logic Equations in Sum of Products Form • Systematic way to obtain logic equations from a given truth table. • PLA – structured logic implementation inputs outputs x 1 x 2 x 3 y 1 y 2 • A product term is included for each row where y i has value 1 0 0 0 1 1 • A product term includes all input 0 0 1 1 1 Inputs AND gates variables. 0 1 0 0 1 • At the end, all product terms are 0 1 1 1 0 ored 1 0 0 0 1 Product terms 1 0 1 0 1 1 1 0 0 0 Outputs OR gates 1 1 1 1 0 + x 1 *x 2 *x 3 + x 1 *x 2 *x 3 + x 1 *x 2 *x 3 y 1 = x 1 *x 2 *x 3 + x 1 *x 2 *x 3 + x 1 *x 2 *x 3 y 2 = x 1 *x 2 *x 3 + x 1 *x 2 *x 3 + x 1 *x 2 *x 3 g. babic Presentation D 7 g. babic Presentation D 8

Circuit � Logic Equation � Truth Table Minimization Applying Boolean Laws • Consider one of previous logic equations: • For the given logic circuit find its logic equation and truth table. x 1 x 2 x 3 y + x 1 *x 2 *x 3 + x 1 *x 2 *x 3 y 1 = x 1 *x 2 *x 3 + x 1 *x 2 *x 3 x1 1 0 0 0 y 1 0 0 1 = x 1 *x 2 *(x 3 + x 3 ) + x 2 *x 3 *(x 1 + x 1 ) x2 0 0 1 0 = x 1 *x 2 + x 2 *x 3 x3 1 0 1 1 0 1 0 0 1 0 1 0 y = x 1 *x 2 + x 2 *x 3 1 1 0 0 But if we start grouping in some other way we may not end up 1 1 1 1 with the minimal equation. • Note that y column above is identical to y 1 column Slide 7. • Thus, the given logic function may be defined with different logic equations and then designed by different circuits. g. babic Presentation D 9 g. babic Presentation D 10 Minimization Using Karnough Maps (1/4) Minimization Using Karnough Maps (2/4) • Provides more formal way to minimization Grouping ( This step is critical) • Includes 3 steps When two adjacent squares contain 1s, they indicate the possibility of an algebraic simplification and they may be combined in one group of 1. Form Karnough maps from the given truth table. There is one two. Similarly, two adjacent pairs of 1s may be combined to form a group Karnough map for each output variable. of four, then two adjacent groups of four can be combined to form a 2. Group all 1s into as few groups as possible with groups as group of eight, and so on. In general, the number of squares in any valid large as possible. group must be equal to 2 k . Note that one 1 can be a member of more 3. each group makes one term of a minimal logic equation for the than one group and keep in mind that you should end up with as few as given output variable. possible groups which are as large as possible. Forming Karnough maps Finding Product Terms • The key idea in the forming the map is that horizontally and vertically The product term that corresponds to a given group is the product of adjacent squares correspond to input variables that differ in one variables whose values are constant in the group. If the value of input variable only. Thus, a value for the first column (row) can be arbitrary, variable x i is 0 for the group, then x i is entered in the product, while if x i but labeling of adjacent columns (rows) should be such that those has value 1 for the group, then x i is entered in the product. values differ in the value of only one variable. g. babic Presentation D 11 g. babic Presentation D 12

Minimization Using Karnough Maps (3/4) Minimization Using Karnough Maps (4/4) Example 1: Given truth table, find minimal circuit Example 2: x 1 x 2 Example 3: x 1 x 2 x 3 x 4 00 01 11 10 00 01 11 10 x 3 00 1 0 0 0 x 1 x 2 x 3 y 0 1 1 0 1 1 1 0 0 01 0 0 0 1 1 1 0 0 1 x1 x2 0 1 1 0 11 0 0 1 1 00 01 11 10 10 x3 0 0 0 0 0 1 0 0 0 y = x 1 *x 3 + x 2 1 0 0 0 0 1 1 1 y = x 1 *x 2 *x 3 + x 1 *x 2 *x 4 + x 2 *x 3 *x 4 1 1 1 1 0 0 1 0 0 Example 4: 0 1 0 1 x 1 x 2 0 1 1 0 00 01 11 10 x 3 x 4 1 1 1 1 y = x 1 *x 2 + x 2 *x 3 00 0 0 1 1 0 1 0 0 01 y = x 1 *x 4 + x 2 *x 3 *x 4 + x 1 *x 2 *x 3 *x 4 11 1 0 0 1 10 0 0 1 1 g. babic Presentation D 13 Presentation D 14 Decoders 3-Input Full Decoder • A full decoder with n input has 2 n outputs. Let inputs be labeled In 0 , In 1 , In 2 ,..., In n-1 , and let outputs be labeled Out 0 , Out 1 ,..., Out 2n-1 . Input Output • A full decoder functions as follows: Only one of outputs has I2 I1 I0 O7 O6 O5 O4 O3 O2 O1 O0 value 1 (it is active) while all other outputs have value 0. The Out0 0 0 0 0 0 0 0 0 0 0 1 Out1 only output set to 1 is one labeled with the decimal value equal 0 0 1 0 0 0 0 0 0 1 0 Out2 to the (binary) value on input lines. 3 Out3 0 1 0 0 0 0 0 0 1 0 0 Decoder Out4 0 1 1 0 0 0 0 1 0 0 0 Out5 • In general, a decoder with n inputs may have fewer than 2 n 1 0 0 0 0 0 1 0 0 0 0 Out6 outputs. Sometime those are called partial decoders. Decoders 1 0 1 0 0 1 0 0 0 0 0 Out7 with only one output are common. 1 1 0 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 g. babic Presentation D 15 g. babic Presentation D 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.