Formal Verification of Automatic Circuit Transformations for - PowerPoint PPT Presentation

Formal Verification of Automatic Circuit Transformations for Fault-Tolerance Dmitry Burlyaev Pascal Fradet 09/30/15, Austin, TX, USA @ FMCAD'15 Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form

Formal Verification of Automatic Circuit Transformations for Fault-Tolerance Dmitry Burlyaev Pascal Fradet 09/30/15, Austin, TX, USA @ FMCAD'15

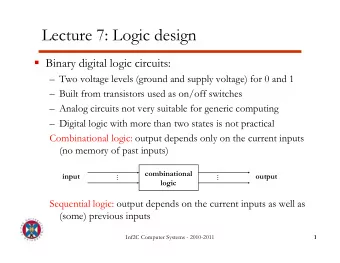

Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form ∀ C : circuit, ∀ i : inputs, ∀ o : outputs, faulty C i − → o ⇒ T [ [ C ] ] i − → o 1/28

Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form ∀ C : circuit, ∀ i : inputs, ∀ o : outputs, faulty C i − → o ⇒ T [ [ C ] ] i − → o ◮ Syntax of circuits 1/28

Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form ∀ C : circuit, ∀ i : inputs, ∀ o : outputs, faulty C i − → o ⇒ T [ [ C ] ] i − → o ◮ Syntax of circuits ◮ Circuit transformations on syntax 1/28

Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form ∀ C : circuit, ∀ i : inputs, ∀ o : outputs, faulty C i − → o ⇒ T [ [ C ] ] i − → o ◮ Syntax of circuits ◮ Circuit transformations on syntax ◮ Semantics of circuits 1/28

Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form ∀ C : circuit, ∀ i : inputs, ∀ o : outputs, faulty C i − → o ⇒ T [ [ C ] ] i − → o ◮ Syntax of circuits ◮ Circuit transformations on syntax ◮ Semantics of circuits ◮ Fault-models described in semantics: bit-flip (SEU), glitch (SET), ... 1/28

Outline For a given (fault-tolerance) transformation T , we want to prove a property of the form ∀ C : circuit, ∀ i : inputs, ∀ o : outputs, faulty C i − → o ⇒ T [ [ C ] ] i − → o ◮ Syntax of circuits ◮ Circuit transformations on syntax ◮ Semantics of circuits ◮ Fault-models described in semantics: bit-flip (SEU), glitch (SET), ... ◮ Case study: our fault-tolerance solution required full confidence 1/28

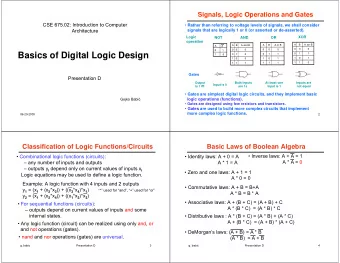

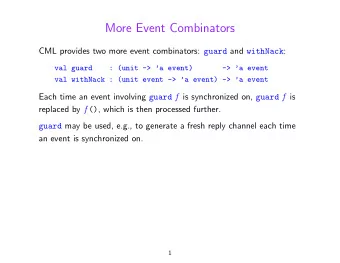

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id 2/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id C ::= Gate | C 1 - - C 2 | [ ] C 1 , C 2[ ] | b − C ◦ 3/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id C ::= Gate | C 1 - - C 2 | [ ] C 1 , C 2[ ] | b − C ◦ C1 C2 3/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id C ::= Gate | C 1 - - C 2 | [ ] C 1 , C 2[ ] | b − C ◦ C1 C2 3/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id C ::= Gate | C 1 - - C 2 | [ ] C 1 , C 2[ ] | b − C ◦ C x 3/28

lddl - language to describe circuits ◮ Gate level HDL ◮ as simple as possible A combinator language (inspired from Sheeran’s µ FP, Ruby, . . . ) Gate ::= not | and | or logic | swap | fork | rsh | lsh wiring id C ::= Gate | C 1 - - C 2 | [ ] C 1 , C 2[ ] | b − C ◦ x − ( swap ) = SWAP x x 3/28

lddl types Bus B := ω | ( B 1 ∗ B 2 ) Gates not : Gate ω ω and , or : Gate ( ω ∗ ω ) ω Plugs ... swap : ∀ α β, Plug ( α ∗ β ) ( β ∗ α ) ... 4/28

lddl types Circuits C ::= ... | C 1 - : ∀ α β γ, Circ α β → Circ β γ - C 2 ◦ → Circ α γ ... | [ ] C 1 , C 2 [ ] : ∀ α β γ δ, Circ α γ → Circ β δ → Circ ( α ∗ β ) ( γ ∗ δ ) ... 5/28

Language feature summary ◮ Correct circuits by construction ◮ correctly connected (typing) ◮ all loops contain a cell (Loop operator) 6/28

Language feature summary ◮ Correct circuits by construction ◮ correctly connected (typing) ◮ all loops contain a cell (Loop operator) ◮ No variables ◮ Simpler semantics (no environment) 6/28

Language feature summary ◮ Correct circuits by construction ◮ correctly connected (typing) ◮ all loops contain a cell (Loop operator) ◮ No variables ◮ Simpler semantics (no environment) ◮ We represent the state (FF values) by circuit itself ◮ e.g., ( false − swap ) true → ( true − swap ) 6/28

lddl semantics of a clock cycle w/o fault A predicate: step C a b C ′ C - an original circuit; a - an input b - an output; C ′ - resulting state after a cycle ❏ G ❑ a = b Gates & Plugs step G a b G step C 1 a b C ′ step C 2 b c C ′ 1 2 Seq step ( C 1 - - C 2 ) a c ( C ′ - C ′ 2 ) 1 - ◦ ◦ step C 1 a c C ′ step C 2 b d C ′ 1 2 Par ] C ′ 1 , C ′ step [ ] C 1 , C 2 [ ] ( a, b ) ( c, d ) [ 2 [ ] step C ( a, b2s x ) ( b, s ) C ′ s2b s y Loop step x − C a b y − C ′ 7/28

lddl semantics of a clock cycle w/o fault A predicate: step C a b C ′ C - an original circuit; a - an input b - an output; C ′ - resulting state after a cycle ❏ G ❑ a = b Gates & Plugs step G a b G step C 1 a b C ′ step C 2 b c C ′ 1 2 Seq step ( C 1 - - C 2 ) a c ( C ′ - C ′ 2 ) 1 - ◦ ◦ step C 1 a c C ′ step C 2 b d C ′ 1 2 Par ] C ′ 1 , C ′ step [ ] C 1 , C 2 [ ] ( a, b ) ( c, d ) [ 2 [ ] step C ( a, b2s x ) ( b, s ) C ′ s2b s y Loop step x − C a b y − C ′ 8/28

lddl semantics of a clock cycle w/o fault A predicate: step C a b C ′ C - an original circuit; a - an input b - an output; C ′ - resulting state after a cycle ❏ G ❑ a = b Gates & Plugs step G a b G step C 1 a b C ′ step C 2 b c C ′ 1 2 Seq step ( C 1 - - C 2 ) a c ( C ′ - C ′ 2 ) 1 - ◦ ◦ step C 1 a c C ′ step C 2 b d C ′ 1 2 Par ] C ′ 1 , C ′ step [ ] C 1 , C 2 [ ] ( a, b ) ( c, d ) [ 2 [ ] step C ( a, b2s x ) ( b, s ) C ′ s2b s y Loop step x − C a b y − C ′ 9/28

Evaluation of a circuit w/o faults As a predicate from Stream to Stream eval : Circ α β → Stream α → Stream β eval C ′ is os step C i o C ′ Eval eval C ( i : is ) ( o : os ) If C applied to input i → output o and C ′ and if C ′ applied to infinite stream is → stream os ⇒ evaluation of C with stream ( i : is ) → stream ( o : os ). 10/28

lddl semantics of a cycle with a fault SET (1 , K )::”at most 1 glitch within K clock cycles” Signal := 0 | 1 | ✒ ◮ Evaluation with glitches is non deterministic ◮ not deterministically latched (as true or false ) by cells ◮ can be be logically masked ( e.g., and (0 , ✒ ) = 0 , . . . ) A predicate: stepg C a b C ′ C - an original circuit; a - an input b - an output; C ′ - possibly corrupted state after a cycle with a glitch at any wire 11/28

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.