Assignment 1 Design module FA(a,b,c,sum,carry) //inputs input - PDF document

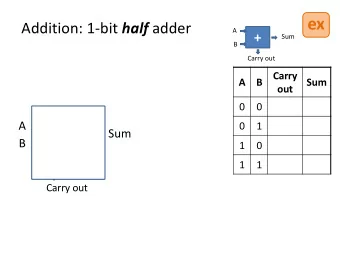

Assignment 1 Design module FA(a,b,c,sum,carry) //inputs input a,b,c //outputs output sum,carry //full adder assignments. assign sum=(a^b^c) assign carry=((a&b)|(b&c)|(c&a)) endmodule module multiplier(output [5:0] P,

Assignment 1 Design module FA(a,b,c,sum,carry); //inputs input a,b,c; //outputs output sum,carry; //full adder assignments. assign sum=(a^b^c); assign carry=((a&b)|(b&c)|(c&a)); endmodule module multiplier(output [5:0] P, input [2:0] a, input [2:0] b); wire zero; //the partial products are given below wire a0b0, a1b0, a2b0; wire a0b1, a1b1, a2b1; wire a0b2, a1b2, a2b2; wire c0, c1, c2, c3, c4; wire s0, s1; assign zero = 1'b0; //andgate instantiations and a1(a0b0,a[0],b[0]); and a2(a1b0,a[1],b[0]); and a3(a2b0,a[2],b[0]); and a3(a0b1,a[0],b[1]); and a4(a1b1,a[1],b[1]); and a5(a2b1,a[2],b[1]); and a5(a0b2,a[0],b[2]); and a6(a1b2,a[1],b[2]); and a7(a2b2,a[2],b[2]); //full adders instantiations FA a0(zero, a0b1, a1b0, P[1], c0);

FA a1(a1b1, a2b0, c0, s0, c1); FA a2(a2b1, zero, c1, s1, c2); FA a3(a0b2, s0, zero, P[2], c3); FA a4(a1b2, s1, c3, P[3], c4); FA a5(a2b2, c2, c4, P[4], P[5]); assign P[0] = a0b0; endmodule Testbench module multiplier_tb; reg [2:0] a; reg [2:0] b; wire [5:0]P; parameter STDIN = 32'h8000_0000; integer testid; integer ret; reg [5:0] tmp; multiplier M1(P, a, b); initial begin testid=55; tmp = testid1; a = tmp[5:3]; b = tmp[2:0]; #10; test(); $finish; end task test; begin if(a*b===P) $display("PASS: %0d * %0d = %0d",a,b,P); else $display("FAIL: %0d * %0d != %0d",a,b,P); end

endtask endmodule Assignment 2 Design module fsm1 (clk, rst, in, out); input clk, rst; input in; output reg out; reg [2:0] cState, nState; parameter A = 3'b000; parameter B = 3'b001; parameter C = 3'b010; parameter D = 3'b011; parameter E = 3'b100; parameter F = 3'b101; parameter G = 3'b110; parameter H = 3'b111; always @(posedge clk) begin if(rst == 1) cState <= A; else cState <= nState; end always @(in or cState) begin case(cState) A: if(in == 1) nState = B; else nState = E; B: if(in == 1) nState = F; else nState = C; C: if(in == 1) nState = D;

else nState = G; D: if(in == 1) nState = H; else nState = A; E: if(in == 1) nState = F; else nState = A; F: if(in == 1) nState = B; else nState = G; G: if(in == 1) nState = H; else nState = C; H: if(in == 1) nState = D; else nState = E; default: nState = A; endcase end always @(cState) begin case(cState) A, B, D, F, G, H: out = 0; C, E: out = 1; default: out = 0; endcase end endmodule Testbench module Testbench; reg clk_t, rst_t, in; wire out; parameter STDIN = 32'h8000_0000; integer testid; integer ret; reg [19:0] tmp; reg [20:0] tmp1; reg [20:0] expected;

integer length; integer i; integer pass; fsm1 C1(clk_t, rst_t, in, out); always begin clk_t <= 0; #25; clk_t <= 1; #25; end initial begin testid = 1; reset_now(); case(testid) 1: begin length = 8; tmp = 8'b1010_0111; end 2: begin length = 14; tmp = 14'b1010_0111_0011_10; end 3: begin length = 15; tmp = 15'b1010_0111_0011_100; end 4: begin length = 15; tmp = 15'b1010_0111_0011_101; end 5: begin length = 18; tmp = 18'b100100_100100_100100; end 6: begin length = 19; tmp = 19'b0100100_100100_100100; end 7: begin length=20; tmp = 0; end 8: begin length=20; tmp = {20{1'b1}}; end 9: begin length=20; tmp = {10{2'b10}}; end 10: begin length=20; tmp = {10{2'b01}}; end 11: begin length=15; tmp = {3{5'b00111}}; end 12: begin length=20; tmp = {4{5'b00110}}; end 13: begin length=16; tmp = {2{8'b10110101}}; end 14: begin length=18; tmp = {6{3'b101}}; end 15: begin length=14; tmp = {2{7'b0111010}}; end default: begin $display("Bad testcase id %d",testid); $finish(); end endcase case(testid) 1 : begin expected = 9'b010010000; end 2 : begin expected = 15'b010010000100001; end 3 : begin expected = 16'b0100100001000010; end

4 : begin expected = 16'b0100100001000000; end 5 : begin expected = 19'b0100100100100100101; end 6 : begin expected = 20'b10010010010010010010; end 7 : begin expected = 21'b101010101010101010101; end 8 : begin expected = 21'b000000000000000000000; end 9 : begin expected = 21'b010001000100010001001; end 10 : begin expected = 21'b100010001000100010000; end 11 : begin expected = 16'b1000010000100000; end 12 : begin expected = 21'b100001000010000100001; end 13 : begin expected = 17'b01001000000000100; end 14 : begin expected = 19'b0100100100100100100; end 15 : begin expected = 15'b100000100001001; end endcase shift(); test(); #5; $dumpoff; $finish; end task reset_now; begin rst_t <= 1; #100; rst_t <=0; end endtask task shift; begin // $write("%d",testid); for (i=length1; i>=0; i=i1) begin in = tmp[i]; #50; tmp1[i+1] = out; end #50; tmp1[0] = out;

end endtask task test; begin pass = 1; for(i=length; i>=0; i=i1) begin if(tmp1[i] != expected[i]) pass = 0; end if(pass==1) $write("PASS: Input = "); else $write(" FAIL: Input = "); for(i=length1; i>=0; i=i1) begin $write("%b",tmp[i]); end if(pass==0) begin $write(" Expected = "); for(i=length; i>=0; i=i1) begin $write("%b",expected[i]); end end $write(" Your output = "); for(i=length; i>=0; i=i1) begin $write("%b",tmp1[i]); end $display(); end endtask endmodule Assignment 3 Design `timescale 1ns / 1ns

module D_flip_flop(input clk,input rst,input d,output q); reg q; always @(posedge clk) if (rst==1) begin q <= 1'b0; end else begin q <= d; end endmodule module sequencer(input clk,input rst, output x); wire A,B,C,A_bar,B_bar,C_bar; wire Ain, Bin, Cin; D_flip_flop q0(clk,rst,Ain,A); not(A_bar,A); D_flip_flop q1(clk,rst,Bin,B); not(B_bar,B); D_flip_flop q2(clk,rst,Cin,C); not(C_bar,C); and(Ain,A_bar,C_bar); xor(Bin,A,B); and(Cin,A,B); assign x = A_bar & B_bar & C_bar; endmodule Testbench `timescale 1ns / 1ns module test;

wire out; reg rst; reg clk; parameter STDIN = 32'h8000_0000; integer testid; integer ret; initial clk <= 1'b1; always #5 clk = ~clk; always #10 $display(out); initial begin testid=1; rst=1; #30; rst=0; #120 $finish; end sequencer ab(clk,rst,out); endmodule Assignment 4 Design module fib(input clock, input reset, output [7:0] value); reg [7:0] R1, R2; always @(posedge clock) begin if(reset == 1) begin R1 <= 0; //change ? to an appropriate value R2 <= 1; //change ? to an appropriate value end else begin R1 <= R2;//put an appropriate expression here R2 <= R1+R2;//put an appropriate expression here end end

assign value =R1; //put an appropriate assignment here endmodule Testbench module test; wire [7:0] out; reg rst; reg clk; parameter STDIN = 32'h8000_0000; integer testid; integer ret; integer i; integer reg1, reg2, tmp; initial clk <= 1'b0; always #5 clk = ~clk; initial begin testid = 1; testid = (testid1)*10; rst=0; rst=1; #2 rst=1; #10 rst =0; #testid; reg1 = 0; reg2 = 1; for(i=0; i<testid/10; i=i+1) begin tmp = reg1; reg1 = reg2; reg2 = reg2+tmp; end if(out===reg1) $write("PASS %0d",out); else $display("FAIL: Wrong value %0d after %0d cycles, expecting %0d",out, testid+1,reg1); #testid $finish; end fib ab(clk,rst,out);

endmodule

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Problem 1 Design a Verilog 16-bit adder module module adder (A, B, sum); input [15:0] A, B;](https://c.sambuz.com/1025319/problem-1-design-a-verilog-16-bit-adder-module-module-s.webp)

![Gotta catch 'em all, with D8 and AngularJS We are Drupal developers Employed by Entity[One]](https://c.sambuz.com/1019204/gotta-catch-em-all-with-d8-and-angularjs-we-are-s.webp)