1 When Q 0 is true, the bottom NOR-gate actcs like an Q = 1 when at - PDF document

4 Minterms The majority function A B C M 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 Digitalteknik och Datorarkitektur 5hp 1 0 1 1 The function can be 1 1 0 1 Sekventiella kretsar described by a thruth table. 28

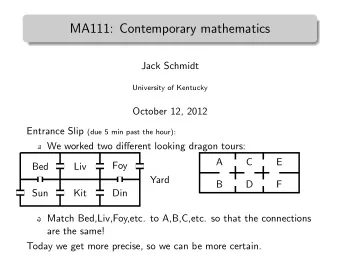

4 Minterms The majority function A B C M 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 Digitalteknik och Datorarkitektur 5hp 1 0 1 1 The function can be 1 1 0 1 Sekventiella kretsar described by a thruth table. 28 april 2008 1 1 1 1 karl.marklund@it.uu.se För en kombinatorisk krets gäller att det existerar en entydig Tools such as Logisim can kombination av utsignal-tillstånd för varje möjlig calculate the thruth table from kombination av insignaler. a circuit ...and minimize the expression En utsignal från en using a Karnaugh map ... Därför kan kombinatorisk krets beror ej kombinatoriska logiska av kretsens historia dvs tidigare in-signalvärden - kretsars funktion kretsen saknar minne ! beskrivas med hjälp av sanningstabeller . ...and build the minimized circuit Är detta en kombinatorisk krets? for us! register a Vi har sett att vi kan 5 bit 32 bit konstruera en ALU register b 5 bit 32 bit Registers med hjälp av kombinatoriska ALU OP kretstar. register c 5 bit 32 bit Vi behöver krestar med minne . Om det var en kombinatorisk krets skulle vi få samma utdata för samma indata varje gång… register a 5 bit 32 bit register b 5 bit 32 32 bit Registers En kombinatorisk krets kan inte ALU OP ha feedback (återkoppling). register c 5 bit 32 bit … och vad är nu det här? På en och samma adress vill vi kunna lagra olika data vid olika tillfällen. 1

When Q 0 is true, the bottom NOR-gate actcs like an Q = 1 when at least one of A and B equals 1 inverter (no matter the value of S) and Q 1 ´ becomes false... Q´ = 1 when both A and B equal 0 A B Q Q´ 0 0 0 1 ... which becomes the input to the top NOR-gate � Q 1 = true = Q 0 (Q is 0 1 1 0 What happens if we change to true here? unchanged) 1 0 1 0 1 1 1 0 Q´ = 0 when at least one of A and B equals 1 Q´ = 0 when at least one of A or B equal 1 A pair of cross-coupled NOR-gates. Deasserting R won’t change anything, Q What happens if we Asserting R will give Q = false... change back to false remains false no matter the value of R. again? ... which becomes the input to the bottom NOR- What happens if we gate � Q’ = true change to true here? ... which becomes the When both R and S are deasserted, the cross-coupled input to the upper NOR- NOR-gats remembers the values of Q and Q´ gate � Q = false What happens if we Again, when both R and S are deasserted, the cross- change S back to coupled NOR-gats remembers the values of Q and Q´ false? ... which becomes the input to the top NOR-gate � Q = true Asserting S gives Q´ = false... Deasserting S won’t change anything... 2

R S Q n+1 Q´ n+1 both zero 0 0 Q n Q´ n 0 1 1 0 R S Q n+1 Q´ n+1 1 0 0 1 1 1 0 0 0 0 Q n Q´ n 0 1 1 0 Overriding the memory feedback action. 1 0 0 1 1 1 ? ? What happens if both R and S drops (voltage change is not instanteneous) to zero simultaneously? Logisim DEMO R drops first... ... resulting in Q = 1 An example of sequential logic : The output output depends not only on the present input but also on the history of the input. R S Q n+1 Q´ n+1 0 0 Q n Q´ n 0 1 1 0 S drops first... ... resulting in Q = 0 1 0 0 1 1 1 Restricted If both R and S drops to zero at the same time � metastability SR Latch R S Q n+1 Q´ n+1 R Q Setting C to 1 will only reset Q if D is 0 at the 0 0 Q n Q´ n same time. D Latch 0 1 1 0 1 0 0 1 Q ´ S D can only function as 1 1 Restricted Set when C (clock/enable) is true. A SR Latch (Set and Reset Latch) can store 1-bit of data. 3

A D Latch (Data Latch) can store C Q 1-bit of data. Q ´ D C D Q n+1 Q´ n+1 Comment C D Q n+1 Q´ n+1 Comment 0 X Q n Q´ n No Change 0 X Q n Q´ n No Change 1 0 0 1 Reset 1 0 0 1 Reset 1 1 1 0 Set 1 1 1 0 Set SR Latch D Latch A latch is a R Q C Q Q´ n+1 C D Q n+1 Q´ n+1 Comment R S Q n+1 sequential device 0 X Q n Q´ n No Change that watches all of its 0 0 Q n Q´ n S Q´ D Q´ 1 0 0 1 Reset inputs continuously 0 0 1 1 and changes its 1 1 1 0 Set 1 1 0 0 outputs at any time. 1 1 Restricted A flip-flop is a sequential device that samples its inputs and changes its outputs only at times D determined by a clocking signal. C D Latch / Flip-Flop C Q C D Q n+1 Q´ n+1 Comment Q 0 X Q n Q´ n No Change D Q´ 1 0 0 1 Reset 1 1 1 0 Set When the latch is open (C=1) Q follows D (a transparent latch) Changing C back to zero… Changing C back to zero… …opens the slave latch taking the Q output of the master latch as D input. The output Q of the master latch follows input D when clock is high (which closes the slave latch). 4

D C D Q n+1 Q´ n+1 Comment C non-falling X Q n Q´ n No Change Q 1 1 0 Set 0 0 1 Reset Output Q only changes on falling clock edges (non transparent). A D Flip-Flop The triangle indicates an edge-trigged latch – a C Q flip flop. The inversion bubble on the clock input indicate a falling-edge Logisim DEMO Q ´ triggered flip-flop D 8 bit D flip-flop register C D Q n+1 Q´ n+1 Comment non-falling X Q n Q´ n No Change 1 1 0 Set 0 0 1 Reset Clock goes Clock 8 D Flip-Flops …output to high... used to form a remains unchanged. 8 bit register. A falling edge 0001 0011 2 trigged D flip-flop 0001 0011 2 C Q D Q´ 5

Clock falls Changing …output …does not back to input .... equals input. affect ouput. low.... 0001 0011 2 1000 1100 2 Funkar bra med multiplexer MEMORY eftersom vi har Address Content relativt få register. I MIPS består 0xFFFFFFFF minnet av 2 32 celler . 0xFFFFFFFE 0xFFFFFFFD Varje cell har en Varje cell i 0xFFFFFFFC unik adress. We have now built minnet kan . a complete lagra åtta bitar, . register file . dvs en byte . . Fyra bytes bildar ett ord 0x00000003 Kan vi bygga register a (word) om 32 3 bit 8 bit minnet på 0x00000002 bitar. register b 3 bit 8 bit samma sätt som Registers 0x00000001 register-filen? ALU OP 0x00000000 register c 3 bit 8 bit 32 stycken MEMORY Address Content 0xFFFFFFFF Giant Multiplexor 0xFFFFFFFE 0xFFFFFFFD 0xFFFFFFFC . . 2 32 stycken . 0x00000003 ...och 32 select Möjligt, men absolut 0x00000002 inte praktiskt att input. bygga ut till 2 32 olika 0x00000001 data inputs... 0x00000000 6

Three State Buffer All inputs share the same output line. A B What happens if we change to 1 E Signals are not 1 here? When not Enabled (E = 0) the or 0.... Signals on three state buffer acts lika a the wire are high A E B huge resistance, kind of or low voltage. 0 (low ) 0 (low) High Z cutting of the wire. 1 (high) 0 (low) High Z We cannot have 0 (low) 1 (high) 0 (low) When Enabled (E = 1) the high and low three state buffer lets the 1 (high) 1 (high) 1 (high) voltage at the input signal A through. same time. Output B can be in three states, 0 (low), 1 E = Error (high) and high resistance (Z). A multilexor A three state buffer Can use three state buffers to acts like a true implement a multiplexor. switch compared to a transistor. A tranistor is never completely off, only the number of electrons used to A shared data form the current can be controlled � line (bus). high or low current 4x2 SRAM Memory 4x4 SRAM Memory Using three state buffer instead of multiplerxors Using three state buffer make it possible to instead of multiplerxors A D Flip-Flop share data lines. make it easy to extend... A shared output data bus. Address line, aka word line . 4x8 bit = 32 bit = 1 Word 7

Static Random Access Memory En kondensator (Capacitor) är som en läckande hink med vatten. Random: takes the same Random ? time to access any Kondensatorn fylls på med random memory location. elektroner och laddas därmed upp. 4x4 SRAM Memory Efter en tid "rinner" ellektronerna ut och kondensatorn tappar sin Static? laddning. Hmm, en kondensator borde kunna användas för att lagra en bit.... Synd bara att den tappar sitt minne efter ett tag... Write: assert word line, drive new value on bit line. Word Line Word Line Capacitor Read: assert word line, sense value on bit line (destroys saved value) Reading a bit destroys the bit � must refresh the memory cell. Asserting both the Word Line and Bit Line Bit Line the Bit Line charges the capacitor bit line word line Word Lines Since real capacitors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically… Bit Cell A latch is …because of this Bit Lines used to refresh requirement, it High remember is a dynamic random Sense Amplifier a whole access memory as opposed to SRAM and word line. Low other static memory Data Address DRAM 8

SRAM DRAM Normal RAM drives many bits (row) out of array, selects few to output. Adding latch at row outputs allows us Stable - holds value as long as Unstable - needs refresh to save an entire row of the RAM power applied Later accesses to the RAM can Faster Slower Latch eliminate the row access time, Less dense (4-6 transistors/bit) High density (1 ransistor/bit) just need column access time More expensive per bit Less expensive per bit Most common in DRAM, page-mode SRAMs also exist Registers must be as fast as possible, hence Flip-Flop memory similar to SRAM is used for registers. Since we use quite a few registers, the low bit denisity does not matter that much. 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.