VLSI Testing Power Aware Serial Scan Virendra Singh Associate - PowerPoint PPT Presentation

VLSI Testing Power Aware Serial Scan Virendra Singh Associate Professor C omputer A rchitecture and D ependable S ystems L ab Department of Electrical Engineering Indian Institute of Technology Bombay http://www.ee.iitb.ac.in/~viren/ E-mail:

VLSI Testing Power Aware Serial Scan Virendra Singh Associate Professor C omputer A rchitecture and D ependable S ystems L ab Department of Electrical Engineering Indian Institute of Technology Bombay http://www.ee.iitb.ac.in/~viren/ E-mail: viren@ee.iitb.ac.in EE-709: Testing & Verification of VLSI Circuits Lecture 25 (21 March 2013) CADSL

T-Flip-Flop based Scan cell for RAS Mudlapur, VDAT’05 To combinational Logic To Bus From Combinational Logic Leading to Primary O/P CLK Row N lines Col N lines ff ff Column Decoder Row Decoder Address {log N } 2 ff CADSL Feb 28, 2012 EE-709@IITB 2

Modified T-Flip-Flip based Cell CLK Single Ended Read Circuits and MISR 0 1 Gandhi, ETS’10 Test Enable Test Control Architecture CTR 1 0 CTR CLK Functional Mode CTR CLK CLK D Q Test Application & Simultaneous Read CTR CLK CLK CLK CLK Reading Response CTR only BIT AOI 1 0 1 0 N lines N lines ff ff 1 Row Decoder Col Decoder READ RA CA CADSL Feb 28, 2012 3 Address

Critical Path Analysis To combinational Logic To Bus From Combinational Logic Leading to Primary O/P CLK TFF Based Scan Cell Row Col CTR D Q D Q CTR CLK MTFF Based Scan Cell CADSL Feb 28, 2012 EE-709@IITB 4

Gate Overhead Circuit #FF #Gates GOV_SS GOVTFF_ GOVMTFF RAS _RAS S5378 179 2779 17.47% 25.3% 20.3% S9234 228 5597 12.04% 17.44% 13.99% S13207 669 7951 21.36% 30.75% 24.6% S15850 597 9772 16.7% 24.15% 19.36% S35932 1728 16065 25.36% 36.4% 29.1% S38417 1636 22179 19.3% 27.8% 22.2% S38584 1452 19253 19.7% 28.3% 22.6% CADSL Feb 28, 2012 EE-709@IITB 5

Efficient Decoder Design Abhishek, ISCAS’10 Optimize the column decoder Uses concept of basis vectors in linear algebra Minimizes the number of linear combinations of basis vectors to generate the transition vectors Directly related to the no. of clock cycles 2-3 times speed up compare to standard RAS CADSL Feb 28, 2012 EE-709@IITB 6

Should Serial Scan Continue? • Three Problems with serial-scan – Test power – Test application time – Test data volume • Efforts and limitations – ATPG for low test power consumption Test power Test length – Reducing scan clock frequency Test power Test application time – Scan-chain re-ordering (with additional logic insertion) Test power/time Design time – Test Compression Test time/data size Has limited capability for Compacted test • Orthogonal attack – Random access scan instead of Serial-scan – Hardware overhead? Silicon cost << Testing cost CADSL 18 Mar 2013 EE-709@IITB 7

Introduction Combinational Block PO PI sff1 sff2 sff3 sff4 sff5 Shift Cycle Capture Cycle CADSL 21 Mar 2013 EE-709@IITB 8

Introduction PO PI Combinational Block sff1 sff2 sff3 sff4 sff5 Initial State 1 1 0 0 1 0 0 0 0 0 Shift Cycle 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 1 0 0 1 0 1 1 0 0 1 Responses 0 1 1 0 0 Capture Cycle CADSL 21 Mar 2013 EE-709@IITB 9

Introduction ● Why, When & How to reduce power during Scan Testing Why ? ➔ Peak Power -- Causes IR-Drop, Cross talk. ➔ Average Power -- Causes excess heat dissipation. When ? Shift Capture Shift & Cycle Cycle Launch CADSL 21 Mar 2013 EE-709@IITB 10

Introduction How ? Test Pattern Pi Response Ri P 1 1 X 1 0 0 R 1 1 0 1 0 1 1 1 1 0 1 1 0 1 P 2 1 0 1 0 1 0 R 2 ➔ Reduce Intra Pattern Transition 0 P 1 1 X 1 0 0 X 1 1 ➔ Reduce Inter Pattern Transition P2 1 0 1 0 1 0 1 0 1 0 1 1 R1 CADSL 21 Mar 2013 EE-709@IITB 11

Problem Formulation Jaynarayan Tudu [ETS 2009] Problem Statement : Determination of the minimum achievable peak power during test for a given test set and find out a test vector sequence which can support the minimum achievable peak power. CADSL 21 Mar 2013 EE-709@IITB

Problem Formulation ● Peak power computation: Test Pattern Response R 2 1 0 1 1 0 Pi Ri R 1 1 0 1 0 0, P 1 1 0 1 0 0, P 2 1 0 1 0 1 Computed Next bit to Transition shifted in 1 P 2 1 0 1 0 0 0 1 1 0 1 0 3 1 0 1 1 0 1 4 0 1 0 1 1 0 4 1 0 1 0 1 1 4 1 0 1 0 1 4 Peak Power = Max V (total transition per clock) = 4 clock CADSL 21 Mar 2013 EE-709@IITB 13

Problem Formulation G raph theoretic problem formulation P 1 P 2 W 12 = 4 V1 V2 V i Nodes are mapped from corresponding test vector W ij = Edge weight = Peak Power = Max V (total transition per clock clock) Direction of edge is mapped from the order of applying the test vectors A Complete directed weighted graph can be formed by applying test vectors in all possible way CADSL 21 Mar 2013 EE-709@IITB 14

Problem Formulation Formulation of Problem1 (Minimal Test time) Problem Statement: Given a complete weighted directed graph Dc , find out a Hamiltonian path which has minimum Path- weight which will be the minimum possible peak power P th1 under minimal test time Definition : Path-weight is defined as the maximum of weight of each edge in the path in a digraph Example : 3 8 10 10 7 V4 V2 V3 V5 V6 V1 path-weight = 10 CADSL 21 Mar 2013 EE-709@IITB 15

Problem Formulation Can we reduce peak power below Pth1 ? Observation : V 2 6 5 7 8 7 V0 V1 V 3 V 5 V 6 9 10 12 V 4 P th 1 = 12 V 2 6 5 7 8 7 V 0 V 1 V 3 V 5 V 6 9 10 12 V 4 CADSL 16

Problem Formulation Can we reduce peak power below P th1 ? Observation : V 2 6 5 7 8 7 V 0 V 1 V 3 V 5 V 6 9 10 12 V 4 Conclusion : There can be a walk which visits every node at least once having walk-weight less than P th1 Definition : walk-weight is defined as the maximum edge-weight in a walk walk-weight = 10 CADSL 21 Mar 2013 EE-709@IITB 17

Problem Formulation Formulation of Problem2 (Reapplication of vectors) Problem Statement: Given an weighted directed graph D , find out a walk which visits each and every nodes at least once and having minimum walk-weight which corresponds to the peak power P th 2 Definition : A walk in D is a non-empty alternating sequence of vertices and edges in D CADSL 21 Mar 2013 EE-709@IITB 18

Problem Formulation How to reduce further below the P th2 ? Observation : V 2 6 5 P th2 = 10 7 8 7 V 0 V 1 V 3 V 5 V 6 9 10 12 V 4 ➔ Further reduction will cause a graph to be disconnected V 2 6 5 7 8 7 V 0 V 1 V 3 V 5 V 6 9 V 4 Maximum edge-weight = 9 CADSL 21 Mar 2013 EE-709@IITB 19

Problem Formulation How to reduce further below the P th2 ? Observation : V 2 6 5 7 8 7 V 0 V 1 V 3 V 5 V 6 9 V 4 Finding out disjoint paths V 2 6 5 Path 1 7 V 0 V 1 V 3 9 V 4 Path 2 Maximum edge-weight = 9 8 V 5 V 6 CADSL 21 Mar 2013 EE-709@IITB 20

Problem Formulation Formulation of Problem3 (Insertion of new vectors) Problem Statement: Find out a path cover for a given directed graph D and join those disjoint paths of path cover in such a way that a complete walk containing all the vertices can be formed which have minimum possible walk-weight less than P th2 . Definition: A path cover of a directed graph D is a set of disjoint paths in D which together contain all the vertices of D CADSL 21

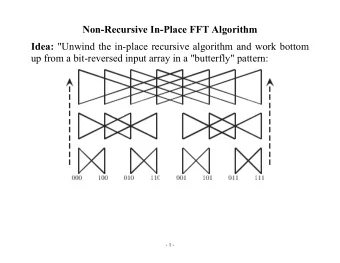

Algorithms Algorithm1 Objective: To find out a hamiltonian path which has minimum Path- weight which will be the minimum possible peak power P th1 under minimal test time for a given complete weighted directed graph Dc , Working principle: Algorithm1 first transform the weighted complete graph into unweighted graph and then it find out the hamiltonian path on unweighted graph which assure the minimum peak power P th1. CADSL 21 Mar 2013 EE-709@IITB 22

Algorithms Example: 1 1 1 0 1 0 1 0 1 1 1 1 0 0 0 R1 1 1 1 1 1 1 1 0 1 0 1 0 1 1 1 P1 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 R2 1 1 1 1 1 1 1 1 1 0 1 0 1 0 1 P2 1 0 1 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 1 R3 P3 1 1 0 1 1 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 R4 P4 14 V1 V2 12 10 8 6 8 7 12 7 7 Do Di 5 5 11 7 3 6 10 10 8 V4 V3 6 7 CADSL 21 Mar 2013 EE-709@IITB 23

Algorithms Step1: Sort the edges in increasing order. Let following be given complete digraph 14 Sorted order of edge weight V1 V2 12 will be: 3,5,6,7,8,10,11,12,14 10 8 6 8 7 12 7 7 Do Di 5 5 11 7 3 6 10 10 8 V4 V3 6 7 CADSL 21 Mar 2013 EE-709@IITB 24

Algorithms Step2: Removing the edges whose weight is greater than next-weight to transform the given complete weighted graph into unweighted graph. next-weight= 8 is chosen using binary search from sorted edge array 3,5,6,7,8,10,11,12,14 V V 14 V V 12 1 1 2 2 10 8 8 6 6 8 8 7 7 12 D D 7 7 7 7 => Di Di o o 5 5 5 5 11 7 7 3 6 3 6 10 10 8 8 V V V V 6 6 4 4 3 3 7 7 CADSL 21 Mar 2013 EE-709@IITB 25

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.