Ultra-Thin Body Self-Aligned I nGaAs MOSFETs on I nsulator (I I I - PowerPoint PPT Presentation

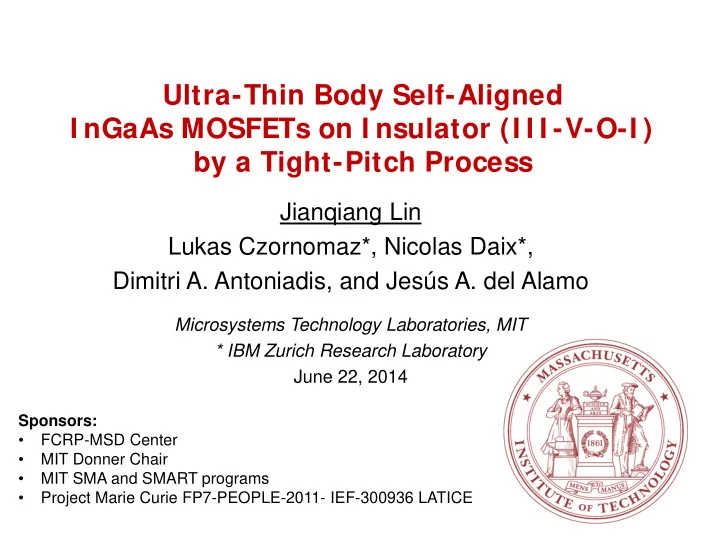

Ultra-Thin Body Self-Aligned I nGaAs MOSFETs on I nsulator (I I I -V-O-I ) by a Tight-Pitch Process Jianqiang Lin Lukas Czornomaz*, Nicolas Daix*, Dimitri A. Antoniadis, and Jess A. del Alamo Microsystems Technology Laboratories, MIT * IBM

Ultra-Thin Body Self-Aligned I nGaAs MOSFETs on I nsulator (I I I -V-O-I ) by a Tight-Pitch Process Jianqiang Lin Lukas Czornomaz*, Nicolas Daix*, Dimitri A. Antoniadis, and Jesús A. del Alamo Microsystems Technology Laboratories, MIT * IBM Zurich Research Laboratory June 22, 2014 Sponsors: • FCRP-MSD Center • MIT Donner Chair • MIT SMA and SMART programs • Project Marie Curie FP7-PEOPLE-2011- IEF-300936 LATICE

Motivation • Superior electron transport properties in InGaAs channel [J. del Alamo, Nature 2011] In 0.7 Ga 0.3 As HEMTs V DS =0.5 V Strained Si Si V DS =1.1-1.3 V 2 2

Si/III-V Integration UC Berkeley [K. Takei, APL 2013] U Tokyo [S. Kim, IEDM 2013] AIST [T. Irisawa, IEDM 2013] MIT / IBM [This work] Contact Gate n+ BOX L c =150 nm p-type Si 3

Substrate Fabrication Following Czornomaz, IEDM 2012 2. H + implants & Al 2 O 3 depo 1. MBE growth BOX: Al 2 O 3 Protection layer: InGaAs Buffer: InAlAs Channel: In 0.7 Ga 0.3 As Si δ -doping: 1x10 12 cm -2 Device layers Stopper: InP n + cap InP buffer/wafer H + InP buffer/wafer 3. Wafer bonding 4. Thermal split InP H + 5. InP etch back H + Device layers BOX BOX BOX p-Si p-Si p-Si 4

Substrate Fabrication 3 nm RMS= 0.25 nm Device layers BOX p-Si 0 2 µ m 0 • Smooth surface of final • Final substrate substrate 5

Device Fabrication Following Lin, IEDM 2013 2. Gate opening, 3. 3-step gate recess, 1. Ohmic/Oxide deposition Mesa isolation Damage anneal SiO 2 W/Mo n + Cap Channel BOX p-Si 4. Gate oxide ALD 5. Gate metal 6. Pad formation Pad Mo HfO 2 Ledge 6

Final Device Structure HfO 2 M1 SiO 2 W/Mo Mo n + cap InGaAs L Ledge Buffer Al 2 O 3 p-Si • Gate dielectric HfO 2 =3.5 nm, EOT=0.7 nm • Intrinsic channel In 0.7 Ga 0.3 As= 8 nm • BOX Al 2 O 3 = 30 nm 7

TEM Cross Sections • Process enables: Tight pitch: L p =150 nm Contact Precise control of ledge: Gate n+ L ledge =30 nm BOX L c =150 nm p p-type Si Mo Contact n+ HfO 2 Mo Gate Channel Buffer BOX L g =50 nm L ledge =30 nm 8

Characteristics of L g = 70 nm MOSFETs V gs -V t =0 to 0.8 V in 0.2V step 250 V ds =0.5 V 400 L g =70 nm L g =70 nm 200 300 I d ( µ A/ µ m) g m ( µ A/ µ m) 150 200 100 100 50 0 0 0.0 0.2 0.4 0.6 -0.4 0.0 0.4 0.8 V ds (V) V gs (V) -4 10 FOM at V ds =0.5 V -5 10 • g m,pk = 309 μ S/ μ m -6 10 I d (A/ µ m) • V t = 96 mV -7 10 • S = 140 mV/dec -8 10 -9 V ds =0.05 and 0.5 V • DIBL = 80 mV/V 10 L g =70 nm -10 • R sd = 1050 Ω.μ m 10 -0.4 0.0 0.4 0.8 9 V gs (V)

I mpact of Back Bias 250 250 250 V bs = -2 V V bs = 0 V V bs = 3 V V gs -V t = 0 to 0.8 V at 0.2 V step 200 200 200 I d ( µ A/ µ m) L g =70 nm I d ( µ A/ µ m) I d ( µ A/ µ m) 150 150 150 100 100 100 50 50 50 0 0 0 0.0 0.2 0.4 0.6 0.0 0.2 0.4 0.6 0.0 0.2 0.4 0.6 V ds (V) V ds (V) V ds (V) Positive V bs : → R on ↓ → I d ↑ → Output conductance ↓ 10

I mpact of Back Bias V bs =3 V V ds =0.5 V 400 -4 10 V bs =0 V L g =70 nm V bs =-2 V -5 10 300 g m ( µ A/ µ m) -6 V bs =3 V 10 I d (A/ µ m) V bs =0 V 200 V bs decreases -7 10 V bs =-2 V -8 10 100 -9 V ds =0.05 and 0.5 V 10 V bs decreases L g =70 nm 0 -10 10 -0.4 0.0 0.4 0.8 -0.4 0.0 0.4 0.8 V gs (V) V gs (V) Positive V bs : → V t ↓ → S ↑ → g m ↑ → DIBL ↓ 11

I mpact of Back Bias on V t and R sd 1200 100 V t,sat (mV) [L g =1 µ m] 50 R sd ( Ω.µ m) 1000 0 -50 800 -100 600 -150 -4 -2 0 2 4 V bs (V) • R sd modulation • V t tunability: ∆ V t = 200 mV for ∆ V bs = = ± 4 V 12

I mpact of Back Bias on Subthreshold Swing Poisson-Schrödinger simulation 200 L g =70 nm V bs = - 2 V 1 Buffer HfO 2 V ds =0.5 V V bs = 0 V E c (eV) S min (mV/dec) Channel 175 V bs = 2 V 0 (a) 150 -1 -4 0 4 8 12 16 18 10 x 10 V bs =-2V y (nm) 8 N s =4x10 12 cm -2 125 n (cm -3 ) -2 -1 0 1 2 3 6 V bs (V) 2V 4 2 Positive V bs (b) 0 → S ↑ -4 0 4 8 12 16 y (nm) Positive V bs → Deeper electron centroid in channel

I mpact of Back Bias on DI BL TCAD simulation of space charge 130 Space charge L g =70 nm (cm -3 ) 120 S G D 1x10 18 V ds =0.5 V DIBL (mV/V) 110 BOX 100 depletion region 90 V ds =0.5 V 80 V gs -V t =0.1 V 100 nm p-Si V bs =0 70 -2 -1 0 1 2 3 -1x10 18 V bs (V) Positive V bs Positive V bs → DIBL ↓ → Si space charge region shrinks → Ground plane moves closer to channel 14

CV and Mobility 2.0 2500 1 - 100 kHz 1.5 2000 2 ) V bs =0 V 2 /Vs) C ( µ F/cm V bs =3 V 1500 1.0 e (cm V bs =-3 V 1000 µ 0.5 L g = 1 µ m 500 0.0 0 2 4 6 8 -0.5 0.0 0.5 1.0 12 cm -2 ) N s (x10 V gs (V) • Low frequency dispersion, CET~ 2 nm • Lower mobility for negative V bs → Confinement increases • Front gate leakage < 10 -3 A/cm 2 at V g =1 V 15

Benchmarking of S, DI BL and Mobility 200 Planar III-V-O-I MOSFETs 300 This work (V bs =0 V) Planar III-V-O-I MOSFETs S min (mV/dec) VLSI13 Kim This work (V bs =0) 150 DIBL (mV/V) VLSI12 Kim (InAs) 200 VLSI13 Kim IEDM12 Czornomaz VLSI12 Kim (InAs) APL11 Takei (InAs) IEDM12 Czornomaz IEDM13 Czornomaz 100 100 V ds =0.5 V 0 0.1 1 0.1 1 L g ( µ m) L g ( µ m) 2000 This work (V bs = 0 V) IEDM13 Kim • Excellent S, DIBL and VLSI13 Irisawa VLSI13 Kim[T50] transport properties 1500 2 /Vs) IEDM12 Czornomaz e (cm 1000 µ 12 cm -2 N s =7x10 500 5 10 15 20 50 t ch (nm) 16

Conclusions • Demonstrated self-aligned In 0.7 Ga 0.3 As MOSFETs on III-V-O-I on p-type silicon substrate • Promising performance, need to lower R sd • Back gate bias allows wide tunability of device characteristics 17

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![New FETs [Spectrum 11/2011, 01/2013 and 08/2019] The smaller you make a CMOS transistor, the more](https://c.sambuz.com/1073250/new-fets-s.webp)