Thin pixel assembly fabrication development with backside - PowerPoint PPT Presentation

Thin pixel assembly fabrication development with backside compensation layer R. Bates 1 , C. Buttar 1 , T. McMullen 1 , G. Pares 2 , L. Vignoud 2 , 1. Experimental Particle Physics Group, University of Glasgow, UK G12 8QQ 2. CEA Lti

Thin pixel assembly fabrication development with backside compensation layer R. Bates 1 , C. Buttar 1 , T. McMullen 1 , G. Pares 2 , L. Vignoud 2 , 1. Experimental Particle Physics Group, University of Glasgow, UK G12 8QQ 2. CEA Léti – MINATEC, 17 rue des Martyrs ; F-38054 GRENOBLE - France On behalf of the UK ATLAS Pixel upgrade groups

Contents • Motivation for thin hybrid modules – Material via worked examples – Through silicon vias • Manufacture of hybrid module • Issues with thin chip processing – Existing technology for ATLAS IBL process • Backside dielectric layer bow compensation – Technical motivation – Run though the process – First results 16/05/2014 R. Bates 2

Motivation for thin hybrid modules • Reduced mass of vertex/tracking systems • Interconnect through the readout circuit – Through silicon vias 16/05/2014 R. Bates 3

ATLAS Phase-II Tracker Upgrade All-silicon inner detector (strips + expanded pixel system) Long ¡Barrel ¡Strips ¡ Short ¡Barrel ¡Strips ¡ Occupancy for < µ >=200 (in %) Forward ¡Strips ¡ Barrel ¡pixel ¡ Forward ¡pixel ¡ ATLAS Letter of Intent Baseline LoI layout of the new ATLAS inner tracker for HL-LHC CERN-2012-022 Aim to have at least 14 silicon hits everywhere (robust tracking) LHCC-I-023 16/05/2014 R. Bates 4

ATLAS Phase-II Tracker Upgrade All-silicon inner detector (strips + expanded pixel system) Long ¡Barrel ¡Strips ¡ Short ¡Barrel ¡Strips ¡ Occupancy for < µ >=200 (in %) Forward ¡Strips ¡ Barrel ¡pixel ¡ Forward ¡pixel ¡ ATLAS Letter of Intent Baseline LoI layout of the new ATLAS inner tracker for HL-LHC CERN-2012-022 Aim to have at least 14 silicon hits everywhere (robust tracking) LHCC-I-023 16/05/2014 R. Bates 5

Phase-II pixel system in numbers 7.8m 2 of Silicon hybrid pixel modules Outer radii: 2 layers Layer 3 & 4: 2940 4-chip modules Issues: large scale production of cheap thinned modules 1.7x10 15 n/cm 2 ; 0.9MGy Forward pixels 16 rings per side 1680 4-chip modules Issues: large scale Inner radii: 2 layers production of cheap thinned Layer 1: 352 2-chip modules modules Layer 2: 576 4-chip modules 1.8x10 15 n/cm 2 ; 0.9MGy Issues: radiation damage & small pixels 1.4x10 16 n/cm 2 ; 7.7MGy 16/05/2014 R. Bates 6

Outer radii pixel system • Pixel modules should be • 2 outer Barrel layers & Disks – Large with high active fraction – Sensor planar n-in-p – Match to FE-I4 geometry ~ 2x2cm 2 – Small contribution to material budget – Pixel size 50 µm x 250 µm – Radiation tolerant – 2x2 FE-I4 (Quad) ~4x4cm 2 – Highly granular – Aim for sensor & ROIC thickness – Optimised for production ~150 µm each Phase-II upgrade ATLAS Current ATLAS 16/05/2014 R. Bates 7

Material and Si Module fraction module silicon Material of a ring module other Total = 2.02% X0 cables and tabs EOS card Front End Plate Rear End Plate Outer Cylinder Middle Cylinder Inner Cylinder Outer Rings structure Middle Rings Inner Rings 10% Fraction of a Radiation Length 9% 8% 7% • 200um ROIC, 300um sensor 6% • Ti Pipe 5% – OD 2.275mm / ID 2.000mm 4% • Carbon foam supports 3% – 4.6mm carbon foam (0.36gcm -3 ) 2% – 0.13mm CFRP facings on both 1% sides ( FAW=100gcm -2 ) 0% 1.74 1.82 1.9 1.98 2.06 2.14 2.22 2.3 2.38 2.46 2.54 2.62 2.7 2.78 2.86 2.94 3.02 3.1 3.18 3.26 3.34 3.42 3.5 3.58 • Silicon = 30% of ring! Pseudo-rapidity 16/05/2014 R. Bates 8

CLIC Vertex detector material • Single point resolution ≈ 3-5 µm – Vertexing & momentum measurement • 0.2% X0/layer including supports Single point Multiple • Air cooled resolution scattering term • Hybrid Pixel module: – Fully depleted : Time slicing (~ 10ns) for background reduction – Fast sparsified read-out – High single point resolution (3µm) : 20x20 µm2 pixel sizes • CLICpix 50um thick ROIC and 50um thick sensor 16/05/2014 R. Bates 9

Through Silicon Vias (TSV) advantages • TSVs connect readout chips to the PCB: easy to tile chips on all 4 sides, fill factor close to 100%. – Distributed periphery removes EOCL dead area • TSV – Almost negligible inductance -> good for fast digital signals – Resistance: <100mOhm/TSV (20mOhm with wirebonds) • Many contacts distributed across the chip à much smaller chip IR drop. • TSV last process preferred – Removes requirement on CMOS vendor • High aspect ratio (5:1) vertical side wall TSV 16/05/2014 R. Bates 10

TSV options Via 40 µm OD -> 120 µm substratee 16/05/2014 R. Bates 11

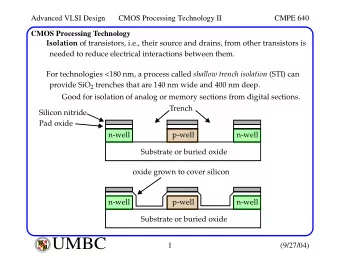

Process stages for 2.5/3D chip stacking AR 1:1 AR 2:1 AR 3:1 u TSV Last u Interconnections u Under Bump Metallurgy (UBM) u Redistribution layer (RDL) u Stacking 16/05/2014 R. Bates 12

Combine technologies for greater functionality TSV and micro-bump stack detail Solder bumps TSV 16/05/2014 R. Bates 13

Bump deposition process 1. Wafer cleaned & inspected 2. TiW/Cu seed layer for UBM 3. Photolithography 4. Electroplating Cu (Ni) UBM/Pillar 5. Solder deposited on top of UBM 1. Different alloys available 6. Photoresist stripped 7. Seed layers wet etched away 8. Bump formed and isolated 9. Solder reflow– a flux-free process Solder bumping using 1. Solder reflow done in reducing gas electroplating in a single mask ambient processes 16/05/2014 R. Bates 14

Flip-chip process • Different bump structures possible: – Structure #1: ROIC: Cu/SnAg – Sensor: thin film UBM – Structure #2: ROIC: Ni/SnPb – Sensor: Ni/SnPb 240C Structure #1, Cu/SnAg Structure #2 solder bumps structure and pillars bonded against Pt assembly sequence UBM 16/05/2014 R. Bates 15

Room Temperature Indium bump bonding • Indium bump bonding can be done at room temperature – Avoids issues with ROIC bowing • Process: – Thick photoresist – Cr UBM process – thermal evaporation – Indium deposition – thermal evaporation 22micron ¡bumps ¡grown ¡ – Lift-Off using ¡evaporator ¡and ¡ – Flip-chip formed ¡using ¡reflow ¡oven ¡ at ¡RAL ¡ • 99.9% Electrical yield – Daisy chain test structures • Produced first FE-I4 module • Good bond yield (>99%) with a few shorts 16/05/2014 R. Bates 16

Simply process thin wafer and flip-chip Bump Process Flow • Evaluated bond yield of 1. Deposit UBM and bumps on ROIC thinned single chip module 2. Thin ROIC to 200 µm / Diced – Use noise and cross-talk measurements 3. On vacuum jigs perform flip-chip for tack bond to sensor • Large areas of non-bonded 4. Re-flow in reducing atmosphere in pixels at the corners & edges oven (240C) unsupported – Have 3% to 66% open bumps assembly • 100% Yield for full Self-align bumps thickness devices Obtain good electrical properties Issues with bump yield due to significant bowing of large readout chip 16/05/2014 R. Bates 17

Bow on thin die 260C RT • FE-I4B die • Silicon thickness = 100 µm • Annealed after CMP • TDM data • Bow of die results in low Sn solder bumped assembly yield due to high re-flow temperature 16/05/2014 R. Bates 18

Calculation of bow • 1 µ m thick AlSi deposited on • Simple bi-metallic calculation for a bare Si wafer at 750 µ m uniform thin film layer (<5% • Good linear behavior during substrate thickness) thermal cycle • Stoney’s Equation for film stress • Modulus (from nanoindentation) = 45 Gpa 2 σ f = E s t s • CTE is estimated ~ 18 ppm 6 R t f 32 • From CTE miss-match 28 24 Warpage ( µ m) ( ) Δ T 20 σ f = E f α f − α s 16 12 8 L 2 E f Δ α Δ Tt f B = 3 4 0 -4 0 50 100 150 200 250 300 2 4 t s E s -8 Temperature (C) -12 -16 • Keep Δ T small for t s thin -20 Well modeled 16/05/2014 R. Bates 19

More complex ROICs • Model can be extended to • Die has many layers with cover many layers with different mask densities differing mask densities – Also film thickness 16% of – But need to know details substrate • For n layers with γ % coverage per layer " % B tot = 3 L 2 n E f ( i ) α f ( i ) t f ( i ) Δ T f ( i ) ∑ ∼ 16 µ m γ f ( i ) $ ' 2 4 E s t s # & i = 1 • With lack of knowledge eventually measure die bow • Model effect of extra well SEM x-section of FE chip showing characterized deposited the full front-side CMOS stack and differing metal densities through the layers layers 16/05/2014 R. Bates 20

FE-I4B 100 µm thick with no stress compensation 25C 260C 200 µm 260C 260C 20 µm 25C 16/05/2014 R. Bates 21

TDM Measurements of 100 µ m thick FEI4B Die thermally cycled 3 times RT to 260C Non-linear deformation with temperature 125 Bow sign change with increasing temperature 100 75 50 Start 25 Warpage ( µ m) 0 0 20 40 60 80 100 120 140 160 180 200 220 240 260 280 -25 Temperature (C) -50 -75 -100 -125 -150 -175 -200 Bare Die 16/05/2014 R. Bates 22

How to live with bow issue • Temporary bond thinned • No open bonds ROIC (150 µm) to thick glass support wafer • Process wafer and flip- Glass support wafer chip • Laser Release support wafer • Used for IBL – <300 modules • Limitations – speed & cost of processes 90 µm ROIC – Heat, laser/UV glue removal, melts bumps with very thin ROIC 16/05/2014 R. Bates 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.