Testability L Lecture 7: Fault Simulation t 7 Shaahin Hessabi - PowerPoint PPT Presentation

Testability L Lecture 7: Fault Simulation t 7 Shaahin Hessabi Shaahin Hessabi Department of Computer Engineering Sharif University of Technology Adapted from the presentation prepared by book authors Slide 1 of 31 Sharif University of

Testability L Lecture 7: Fault Simulation t 7 Shaahin Hessabi Shaahin Hessabi Department of Computer Engineering Sharif University of Technology Adapted from the presentation prepared by book authors Slide 1 of 31 Sharif University of Technology Lecture 6: Fault Simulation

O tli Outline � Problem and motivation � Fault simulation algorithms � Serial � Parallel � Parallel � Deductive � Concurrent � Random Fault Sampling � Summary Slide 2 of 31 Sharif University of Technology Lecture 6: Fault Simulation

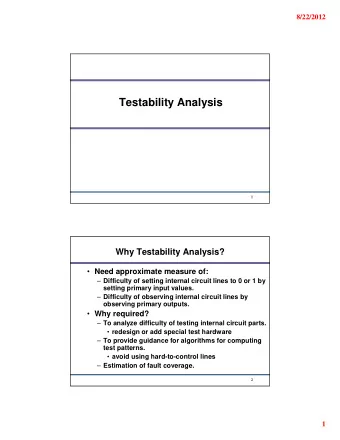

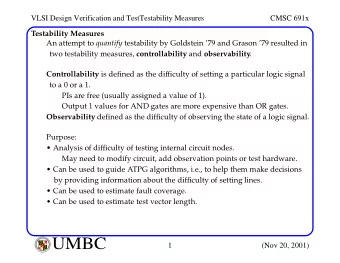

Problem and Motivation � Fault simulation Problem: � Given: � A circuit � A sequence of test vectors � A fault model � A fault model � Determine: � Fault coverage: fraction (or percentage) of modeled faults detected by test vectors � Set of undetected faults (for test generation) � Motivation � Determine test quality and in turn, product quality � Find undetected fault targets to improve tests � Construct fault dictionary for diagnosis � Construct fault dictionary for diagnosis – Use a fault simulator to compute & store the response for every fault – If the output response of the circuit under test matches any of the response in the fault dictionary the fault location is identified response in the fault dictionary, the fault location is identified Slide 3 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Yield and Defect Level � Let: � Y (yield): probability that a manufactured circuit is defect-free � Y (yield): probability that a manufactured circuit is defect free � D L (defect level): probability of shipping a defective product � d (defect coverage): the defect coverage of the test used to check for manufacturing defects manufacturing defects � D L = 1- Y 1 d � D = 1 Y 1-d Defec approximate defect coverage with fault coverage with fault coverage ct Level Defect Coverage % Slide 4 of 31 Sharif University of Technology Lecture 6: Fault Simulation

High Fault Coverage: Why? g g y Slide 5 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Fault Coverage vs. Defect Coverage � High fault coverage (measured for SSFs) is: g g ( ) necessary but not sufficient for high defect coverage. � Also need: � Parametric testing � Delay-fault testing � Bridging fault testing � Bridging-fault testing � Technology-specific-fault testing (e.g., CMOS stuck-open faults) Slide 6 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Fault simulator in a VLSI Design g Process Verification Verified design input stimuli netlist Fault simulator Test vectors Modeled Test Remove Delete fault list compactor vectors tested faults Fault Low Test coverage generator Add vectors ? Adequate q Stop Slide 7 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Fault Simulation Scenario au t S u at o Sce a o � Circuit model: mixed-level � Mostly logic with some switch level for high impedance (Z) and � Mostly logic with some switch-level for high-impedance (Z) and bidirectional signals � High-level models (memory, etc.) with pin faults � Signal states: logic � Two (0, 1) or three (0, 1, X) states for purely Boolean logic circuits � Four states (0, 1, X, Z) for sequential MOS circuits � Timing: � Zero-delay for combinational and synchronous circuits � Mostly unit-delay for circuits with feedback Slide 8 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Fault Simulation Scenario (cont’d) Fault Simulation Scenario (cont d) � Faults: � Mostly single stuck-at faults � Sometimes stuck-open, transition, and path-delay faults; analog circuit fault simulators are not yet in common use i it f lt i l t t t i � Equivalence fault collapsing of single stuck-at faults � Fault-dropping: a fault once detected is dropped from consideration � Fault dropping: a fault once detected is dropped from consideration as more vectors are simulated; fault-dropping may be suppressed for diagnosis � Fault sampling: a random sample of faults is simulated when the F lt li d l f f lt i i l t d h th circuit is large Slide 9 of 31 Sharif University of Technology Lecture 6: Fault Simulation

F Fault Simulation Algorithms lt Si l ti Al ith � Serial � Parallel P ll l � Deductive � Concurrent C t Slide 10 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Serial Algorithm � Algorithm: Simulate fault-free circuit and save responses. Repeat following steps for each fault in the fault list: Repeat following steps for each fault in the fault list: � Modify netlist by injecting one fault � Simulate modified netlist, vector by vector, comparing responses y p g p with saved responses � If response differs, report fault detection and suspend simulation of remaining vectors remaining vectors � Advantages: � Easy to implement; needs only a true-value simulator less memory � Easy to implement; needs only a true value simulator, less memory � Most faults, including analog faults, can be simulated Slide 11 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Serial Algorithm (Cont.) � Disadvantage: Much repeated computation; CPU time g p p prohibitive for VLSI circuits � Alternative: Simulate many faults together Test vectors Fault-free circuit Comparator f1 detected? Circuit w ith fault f1 Comparator f2 detected? Circuit w ith fault f2 Comparator fn detected? Circuit w ith fault fn Slide 12 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Parallel Fault Simulation � Compiled-code method; best with two-states (0,1) � Exploits inherent bit-parallelism of logic operations on computer words � Storage: one word per line for two-state simulation; i.e., fixed low memory requirement � Multi-pass simulation: Each pass simulates w -1 new M lti i l ti E h i l t 1 faults, where w is the machine word length � Speed up over serial method � Speed up over serial method ~ w -1 w 1 � Not suitable for circuits with timing-critical and non- Boolean logic Boolean logic Slide 13 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Parallel Fault Simulation Example Parallel Fault Simulation Example Bit 0: fault-free circuit Bit 1: circuit with c s-a-0 Bit 2: circuit with f s-a-1 1 1 1 c s-a-0 detected 1 0 1 a 1 0 1 1 1 1 e b 1 0 1 c s-a-0 g g 0 0 0 d d s-a-1 s a 1 f f 0 0 0 1 0 1 Slide 14 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Parallel Fault Simulation- Multiple Values � Three signal values : { 0 1 u } � Three signal values : { 0, 1, u } A A A1 A1 A0 A0 � Two bits per signal encoding: 0 0 0 1 1 1 U 1 0 Slide 15 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Deductive Fault Simulation Deductive Fault Simulation � One-pass simulation p � Each line k contains a list L k of faults detectable on k; i.e., fault F in list L k ⇔ F causes signal k be sensitized k � Following true-value simulation of each vector, fault lists of all gate output lines are updated using set-theoretic rules, signal values, and gate input fault lists � PO fault lists provide detection data � Limitations: � Set-theoretic rules difficult to derive for non-Boolean gates � Gate delays are difficult to use G t d l diffi lt t Slide 16 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Deductive Fault Simulation (cont’d) � AND gate Any fault causes an error at A or B (change A or B � from 1 to 0) will cause Z to be erroneously 0. � L Z = L A ∪ L B ∪ {Z s-a-0} { } Z A B � Any fault that causes A to be 1 without changing B, will cause Z to be in error ; i e Z will cause Z to be in error ; i.e, Z = 1 1 � L Z = (L A ∩ L’ B ) ∪ {Z s-a-1} = (L A − L B ) ∪ {Z s-a-1} Slide 17 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Deductive Fault Simulation (cont’d) � Gate Z: � I: set of inputs I f i � c: controlling value � i: inversion � i: inversion � S: set of inputs with values c � The fault list of Z: � If no input has value c, any fault effect on any input propagates to the output. p � If some inputs have value c, only a fault effect that affects all the inputs at c without affecting any of the inputs at c propagates to the output. Slide 18 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Deductive Fault Simulation (Example) ( p ) Notation: L k is fault list for line k k n is s-a-n fault on line k L e = L a U L c U {e 0 } {a 0 } 1 = {a 0 , b 0 , c 0 , e 0 } a {b 0 , c 0 } 1 e e 1 b b 1 c c {b 0 } g g g f f 0 d d U L g = (L e L f ) U {g 0 } {b 0 , d 0 } {b 0 , d 0 } = {a 0 , c 0 , e 0 , g 0 } { } {b 0 , d 0 , f 1 } Faults detected by the input vector the input vector Slide 19 of 31 Sharif University of Technology Lecture 6: Fault Simulation

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.