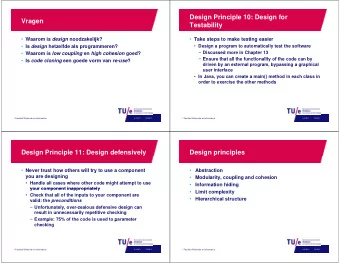

21. Design for Testability 40 J. A. Abraham 60 Department of - PowerPoint PPT Presentation

mm 40 60 80 100 120 21. Design for Testability 40 J. A. Abraham 60 Department of Electrical and Computer Engineering The University of Texas at Austin VLSI Design Fall 2015 80 November 11, 2015 ECE Department, University of Texas at

mm 40 60 80 100 120 21. Design for Testability 40 J. A. Abraham 60 Department of Electrical and Computer Engineering The University of Texas at Austin VLSI Design Fall 2015 80 November 11, 2015 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 1 / 51

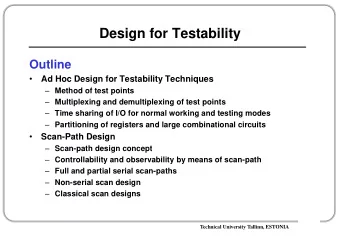

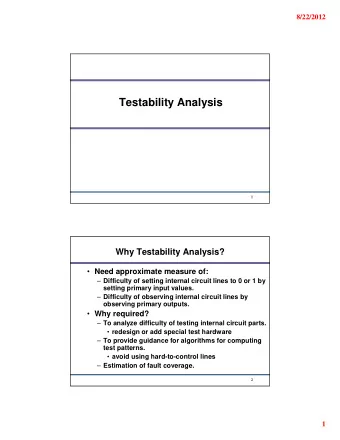

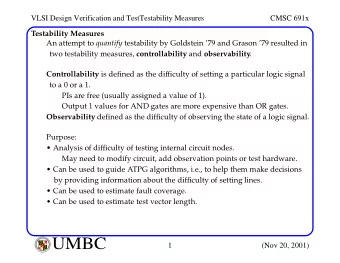

Design for Testability (DFT) mm 40 60 80 100 120 Reduce costs associated with testing complex circuit Design circuit so that it will be easier to test Increase accessibility of internal nodes 40 Controllability: ability to establish specific signal value at each internal node by setting inputs Observability: ability to determine internal values by controlling inputs and observing outputs Ensure predictable circuit responses 60 Tradeoffs Technical: area, I/O pins, performance Economic: design time, yield, time to revenue 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 1 / 51

Testable Sequential Circuits Sequential circuits are very difficult to test mm 40 60 80 100 120 40 Design the internal memory elements to be part of a shifter register chain to provide controllability, 60 observability through serial shifts 80 With scan chain , problem of testing any circuit reduces to testing the combinational logic ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 2 / 51

Level-Sensitive Scan Design (LSSD) mm 40 60 80 100 120 Structured DFT developed at IBM All internal storage implemented in hazard-free polarity-hold latches (SRLs) , part of a scan chain Latches controlled by two or more non-overlapping clocks , 40 with rules for clocking All clock inputs to SRLs must be in their off states when primary inputs (PIs) are “off” Clock signal at any clock input to an SRL must be controlled 60 from one or more clock PIs No clock can be ANDed with another clock Clock PIs cannot feed data inputs to latches, either directly or through combinational logic 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 3 / 51

Scan Chains Convert each flip-flop to a scan register Only costs one extra multiplexer mm 40 60 80 100 120 Normal mode: flip-flops behave as usual Scan mode: flip-flops behave as shift register Contents of flops can be scanned out and new values scanned in 40 60 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 4 / 51

Scannable Flip-Flops mm 40 60 80 100 120 40 60 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 5 / 51

Boundary Scan mm 40 60 80 100 120 Testing boards is also difficult Need to verify solder joints are good Drive a pin to 0, then to 1 Check that all connected pins get the values 40 Single-sided PC boards with “through-hole” construction used “bed of nails” to contact pins of chip on the back side of the board SMT and BGA boards cannot easily contact pins 60 Build capability of observing and controlling pins into each chip to make board test easier 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 6 / 51

Boundary Scan (IEEE 1149.1) mm 40 60 80 100 120 40 60 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 7 / 51

Boundary Scan Example mm 40 60 80 100 120 40 60 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 8 / 51

Boundary Scan Interface mm 40 60 80 100 120 Boundary scan is accessed through five pins TCK: test clock TMS: test mode select 40 TDI: test data in TDO: test data out TRST*: test reset (optional) Chips with internal scan chains can access the chains through 60 boundary scan for unified test strategy 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 9 / 51

I DDQ Testing mm 40 60 80 100 120 Measure quiescent power supply current of CMOS circuits for selected test vectors Example, microprocessor has nanoamps of current with no faults; many defects (shorts, for example) cause much higher 40 currents Direct relationship found (Sandia Labs., HP, Phillips) between IDDQ test acceptance rates and quality, reliability of ICs Only need to activate site of potential defect (no need to 60 propagate errors) Leakage current in very large chips may overwhelm the abnormal current due to a fault in one gate 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 10 / 51

I DDQ Testing, Cont’d mm 40 60 80 100 120 40 60 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 11 / 51

Built-In Self Test (BIST) mm 40 60 80 100 120 Increasing circuit complexity, tester cost Interest in techniques which integrate some tester capabilities on the chip Reduce tester costs 40 Test circuits at speed (more thoroughly) Approach: Compress test responses into “signature” Pseudo-random (or pseudo-exhaustive) pattern generator 60 (PRG) on the chip Integrating pattern generation and response evaluation on chip – BIST 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 12 / 51

Pseudo-Random Sequence Generator (PRSG) Linear Feedback Shift Register mm 40 60 80 100 120 Shift register with input taken from XOR of state Pseudo-Random Sequence Generator (or Pseudo-Random Pattern Generator (PRPG), or Linear Feedback Shift Register (LFSR)) 40 Step Q 0 111 1 110 2 101 60 3 010 4 100 5 001 6 011 80 7 111 (repeats) ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 13 / 51

Example of BIST mm 40 60 80 100 120 40 60 Technique called STUMPS (from IBM) 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 14 / 51

Testability Issues – Custom Microprocessors mm 40 60 80 100 120 Chip complexity, large volumes, costs Area/performance penalties Fault (defect) coverage goals 40 Test generation (fault simulation) costs Development time Tester time (manufacturing costs) 60 ASICs generally use a “full scan” methodology for testability Some of the ad-hoc techniques used in custom microprocessors will be described in the following slides 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 15 / 51

Testability Features of the Motorola 68020 Chip Statistics: mm 40 60 80 100 120 Process: 2 µ HCMOS Die Size: 375 × 347 mils Transistor count: 200K Test Overhead 40 Test Logic Area: < 3% Test Microcode: < 2% Test routing shared with functional routing to keep chip area down Bus structure helped create test partitioning for embedded 60 structures Tradeoff of extra time to produce ad-hoc test logic with expected higher yield Test techniques for ROMs, PLAs, Cache 80 Test mode not available to customers (Why??) ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 16 / 51

Testing Scheme for ROMs in the 68000 Family mm 40 60 80 100 120 Initial schemes for testing 68000 family control structures involved bussing nanoROM outputs off-chip via the address bus in test mode 40 Could not test at speed since nanoROM output buffers were not sized to drive a bus Only nanobits were observable, and the PLAs, microROM and nanoROM had to be tested as one large sequential machine 60 Test sequences were lengthy and difficult to write Tests were also microcode dependent 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 17 / 51

Testability Techniques for 68020 ROMs Used test mode to force next microcode address (NMA) from mm data pins 40 60 80 100 120 Data pins also control a MUX for both micro and nano ROM outputs, which are moved to the BC bus, into the data section of the execution unit, and to the address bus which can be observed 40 Exhaustive testing of the 2K ROM entries 60 32 bits of ROM visible every 2 clocks Four passes of tests needed to read the 110 80 outputs of the two ROMs ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 18 / 51

Microrom Test in MC68881 Floating Point Co-processor ROM physically split into two sections In test mode, ROM is addressed directly through the mm command register 40 60 80 100 120 Exhaustive addresses fed to ROM in a “ping-pong” fashion (address/address complement) Outputs of ROM go to two 16-bit signature registers (using CCITT-16 polynomial x 15 + x 12 + x 5 + 1 ) 40 Monitor both the quotient and final signature serially on a test pin (Probability of aliasing 2 − ( n + m − 1) ) 60 80 ECE Department, University of Texas at Austin Lecture 21. Design for Testability J. A. Abraham, November 11, 2015 19 / 51

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.