Design for Testability (DFT) Sh Sh Shaahin Hessabi Shaahin - PowerPoint PPT Presentation

Testability: Lecture 23 Design for Testability (DFT) Sh Sh Shaahin Hessabi Shaahin Hessabi hi hi H H bi bi Department of Computer Engineering Department of Computer Engineering Sharif University of Technology Sharif University of

Testability: Lecture 23 Design for Testability (DFT) Sh Sh Shaahin Hessabi Shaahin Hessabi hi hi H H bi bi Department of Computer Engineering Department of Computer Engineering Sharif University of Technology Sharif University of Technology Adapted, with modifications, from lecture notes prepared by the Adapted, with modifications, from lecture notes prepared by the p p , , , , p p p p y y book authors book authors Slide 1 of 43

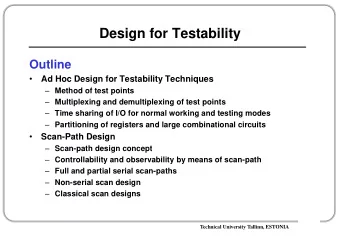

Outline � Iterative Logic Arrays Iterative Logic Arrays � Ad Ad- -hoc DFT methods hoc DFT methods � Scan design Scan design g � Design rules Design rules � Scan register Scan register Scan register Scan register � Scan flip Scan flip- -flops flops � Scan test sequences Scan test sequences � Overheads Overheads � Scan design system Scan design system Testability: Lecture 23 Sharif University of Technology Slide 2 of 43

Iterative Logic Arrays (ILAs) � Some circuits are easy to test, for example, ILAs � Definition: An ILA is a k -dimensional array-like circuit composed e o s a d e s o a a ay e c cu co posed of identical cells with uniform interconnections � Array circuits can be tested for powerful fault models using relatively few tests relatively few tests � Examples: � Arithmetic circuits � Arithmetic circuits � Ripple-carry adders � Array multipliers � Array multipliers � Bit-sliced processors � Random-access memories: RAMs, ROMs � Random access memories: RAMs, ROMs � ILA models of sequential circuits Testability: Lecture 23 Sharif University of Technology Slide 3 of 43

Example 1: Ripple-Carry Adder � 1D array composed of full-adder cells Testability: Lecture 23 Sharif University of Technology Slide 4 of 43

Example 1: Ripple-Carry Adder (cont’d) � Assume the cell fault (CF) model, which implies that all single logic faults in all realizations will be detected. i l l i f lt i ll li ti ill b d t t d � We must apply eight patterns to every cell and observe the responses. � Six of the 8 patterns can be applied simultaneously to all cells; e.g., A i B i C i = 000 � Faults in FA i can be observed via S i or C i+1 i i i+1 � Two of the 8 patterns cannot be applied simultaneously to all cells, namely A i B i C i = 001 and 110, because C in ≠ C out y i i i in out Testability: Lecture 23 Sharif University of Technology Slide 5 of 43

Example 1: Ripple-Carry Adder (cont’d) p pp y ( ) � The patterns AiBiCi = 001 and 110 can be applied simultaneously to b li d i l l alternating cells � All CF faults in an n -bit RC adder All CF f lt i bit RC dd can be detected by 8 tests, independent of the array size n. independent of the array size n. � The property of an n -cell ILA that all (cell) faults can be d detected by a constant number test patterns for any n is called d b b f i ll d C-testability Testability: Lecture 23 Sharif University of Technology Slide 6 of 43

Example 2: Gate Array � This is an ILA realization of a k This is an ILA realization of a k- -input AND function, input AND function, k k = = 1 1, ,2 2, ,3 3, , … � Question 1: Is an AND array C : Is an AND array C- -testable? testable? � Question Question2 2: What if the AND function is replaced by : What if the AND function is replaced by XOR? XOR? Testability: Lecture 23 Sharif University of Technology Slide 7 of 43

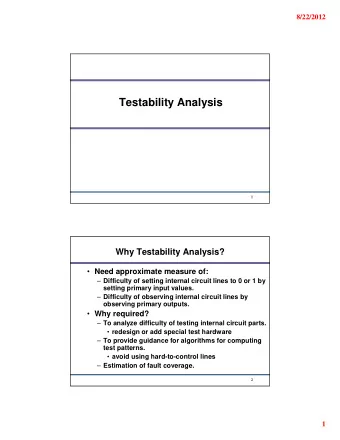

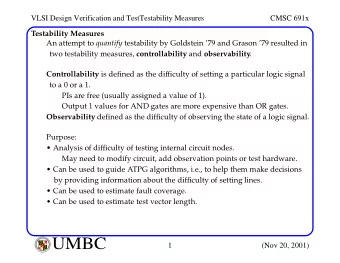

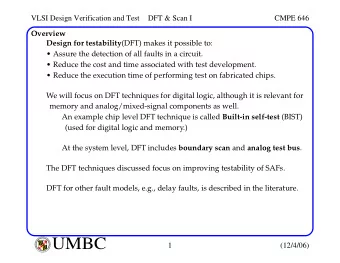

Design for Testability (DFT) � Test generation algorithms for logic circuits are complex Test generation algorithms for logic circuits are complex (NP complete) (NP complete) (NP complete) (NP complete) 10 6 gates or 10 2 flip � Circuits containing, say, Circuits containing, say, 10 gates or 10 flip- -flops, may flops, may be too large for ATPG tools be too large for ATPG tools be too large for ATPG tools be too large for ATPG tools � Heuristic methods are used for testing complex circuits Heuristic methods are used for testing complex circuits such as microprocessors, RAMs, etc. such as microprocessors RAMs etc such as microprocessors RAMs etc such as microprocessors, RAMs, etc. � Fault coverage of such methods can be low and hard to Fault coverage of such methods can be low and hard to dete mine dete mine determine determine � To ensure high levels of testability, design for testability To ensure high levels of testability, design for testability (DFT) is often essential (DFT) is often essential (DFT) i (DFT) i ft ft ti l ti l Testability: Lecture 23 Sharif University of Technology Slide 8 of 43

Testability Goals Maximize fault coverage Maximize fault coverage 1. 1. Minimize test application time Minimize test application time Minimize test application time Minimize test application time 2. 2. 2 Minimize test data size Minimize test data size 3. 3. Minimize test generation effort Minimize test generation effort 4. 4. Testability: Lecture 23 Sharif University of Technology Slide 9 of 43

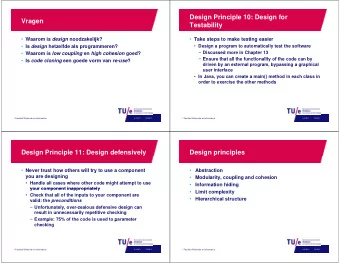

Definition � Design for testability Design for testability (DFT) refers to those design (DFT) refers to those design techniques that make test generation and test techniques that make test generation and test techniques that make test generation and test techniques that make test generation and test application cost application cost- -effective. effective. � DFT methods for digital circuits: � DFT methods for digital circuits: DFT methods for digital circuits: DFT methods for digital circuits: � Ad Ad- -hoc methods hoc methods � � Structured methods: Structured methods: � � Scan Scan � Partial Scan P P Partial Scan i l S i l S � Built Built- -in self in self- -test test (BIST) (BIST) � Boundary scan � Boundary scan Boundary scan Boundary scan Testability: Lecture 23 Sharif University of Technology Slide 10 of 43

DFT � In general, DFT deals with ways for improving In general, DFT deals with ways for improving controllability and observability controllability and observability controllability and observability controllability and observability � Costs associated with DFT: Costs associated with DFT: � Pins � Area/Yield � Area/Yield � Performance � Design time Testability: Lecture 23 Sharif University of Technology Slide 11 of 43

Objections to DFT j � Short-sighted view of management (schedule and costs) g g ( ) � Life-cycle cost ignored by development management/contractors/buyers g / / y � Area/functionality/performance myths � Lack of knowledge by design engineers � Lack of knowledge by design engineers � Testing is someone else’s problem � Lack of tools to support DFT (this is improving….) L k f t l t t DFT (thi i i i ) Testability: Lecture 23 Sharif University of Technology Slide 12 of 43

Ad-Hoc DFT Methods � Good design practices learnt through experience are Good design practices learnt through experience are used as guidelines: used as guidelines: used as guidelines: used as guidelines: ( ⇒ oscillation) � Avoid asynchronous ( Avoid asynchronous (unclocked unclocked) feedback. ) feedback. ( oscillation) � Make flip Make flip- -flops flops initializable initializable. ( . (clear clear or or preset preset) ) � Avoid redundant gates. Avoid large fan Avoid redundant gates. Avoid large fan- -in gates. in gates. (controllability, observability) (controllability, observability) � Provide test control for difficult � Provide test control for difficult Provide test control for difficult-to Provide test control for difficult to to-control signals. to control signals. control signals. control signals. � Avoid gated clocks. Avoid gated clocks. � Consider ATE requirements ( C Consider ATE requirements (tristates C id id ATE ATE i i t t ( (t i t t t i t t tristates, etc.) , etc.) t t ) ) � Design reviews conducted by experts or design Design reviews conducted by experts or design auditing tools. auditing tools. diti diti t t l l Testability: Lecture 23 Sharif University of Technology Slide 13 of 43

Disadvantages of Ad-Hoc DFT Methods � Circuits are too large for manual inspection. Circuits are too large for manual inspection. � � � Experts and tools not always available. Experts and tools not always available. � Test generation is often manual with no guarantee of Test generation is often manual with no guarantee of g g a o a o o o a ua a ua o gua a o gua a o o high fault coverage. high fault coverage. � Design iterations may be necessary. Design iterations may be necessary. Design iterations may be necessary. Design iterations may be necessary. � Use of ad se of ad- -hoc DFT is usually discouraged for large hoc DFT is usually discouraged for large circuits. circuits. circuits. circuits. Testability: Lecture 23 Sharif University of Technology Slide 14 of 43

Ad Hoc Design Rules � Partitioning Partitioning � Insert control/observation points ( Insert control/observation points ( test points test points ), e.g., a ), e.g., a reset line for initialization reset line for initialization � Avoid redundancy Avoid redundancy � Improve circuit structure, e.g., break global feedback Improve circuit structure, e.g., break global feedback during testing during testing � Provide clock access during testing Provide clock access during testing Testability: Lecture 23 Sharif University of Technology Slide 15 of 43

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.