Status of Present Chip Submission M.Winter / CERN, 17th of February - PowerPoint PPT Presentation

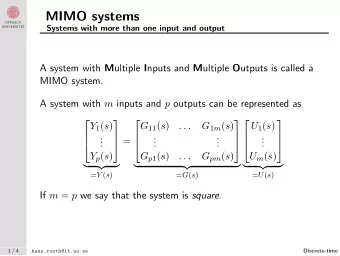

Status of Present Chip Submission M.Winter / CERN, 17th of February 2014 on behalf of the PICSEL & ALICE teams of IPHC/Strasbourg Outline Engineering run overview Overview of FSBB chips Overview of Optimisation & Investigation

Status of Present Chip Submission M.Winter / CERN, 17th of February 2014 on behalf of the PICSEL & ALICE teams of IPHC/Strasbourg Outline Engineering run overview • Overview of FSBB chips • Overview of Optimisation & Investigation Prototypes • MIMOSA-32FEE2/3, MIMOSA-22THRb3, MIMOSA-34b, ... 1

Sensor Development Organisation 2

Engineering Run Status • List of chips : � FSBB-M0a & -M0b: ∼ complete chain of MISTRAL components � FSBB-A0 : ∼ complete chain of ASTRAL components � MIMOSA-32FEE2 : in-pixel circuitry optimisation � MIMOSA-32FEE3 : pixel circuitry without MIM-cap � MIMOSA-22THRb2 : large pixel array with 2-row r.o. & e.o.c. discri. � MIMOSA-34b : large pixels with various dim. & sensing nodes � various test structures : SEL-test array, etc. • Status : � submitted 07/02/2014 � expected return form foundry ∼ mid-May 3

FSBB-M0a/b Overview • Main characteristics : � pixels of 22 × 33 µm 2 including pre-amp. & CDS (clamping) � staggered sensing nodes � double-row rolling shutter read-out ( ≡ MIMOSA-22THRb) � 416 columns of 416 rows � 13.7 × 9.2 mm 2 active area → becomes 13 × 10 mm 2 with 31 × 24 µm 2 pixels ֒ � 3 stages zero-suppression ( ≡ SUZE-02) ֒ → windows of 4 × 5 pixels encoded on 32 bits � 4 output buffers of 512 × 32 bits each � 2 output nodes at 320 Mbits/s (160 MHz clock) � integrated JTAG, regulators, VDD, GND, ... � t r.o. ≃ 35 µs � 2 slightly different sub-arrays in each sensor : optimisation of sensing node geometry & in-pixel circuitry • Design not final, e.g. in terms of : � pixel dimensions � power consumption � SUZE-02 throughput vs power � peripheral circuitry area � pad implementation � trigger implementation 4

FSBB-A0 Overview • Identical to FSSB-M0a except : � in-pixel circuitry incorporates one discriminator � uniform pixel design ( ≡ AROM-1b) � t r.o. � 20 µs • Design not final : � similar degree of finalisation as FSBB-M0a/b � moreover : in-pixel circuitry optimisation (noise suppression) still on-going 5

In-Pixel Circuitry Optimisation • 2 MIMOSA-32 FFE chips � Pixels of 20 × 20/33 µm 2 � 32 sub-arrays of 16 × 64 pixels � Read-out time ≃ 10–13 µs • Parametres modified : � Improve pre-amp performances : ◦ Pre-amp input transistor design against RTS ◦ Pre-amp feedback loop transistors ◦ N-MOS vs P-MOS transistors for gain optimisation � MIM capacitors replaced by MOS capacitors ֒ → avoid using ML5 & ML6 � Simplified low power pre-amp design 6

Validation of Large Pixel Sensor • MIMOSA-22THRb2 chip : � Goal : confirm 2-row read-out performances with large pixels � 64 × 64 pixels of 22 × 66 µm 2 � in-pixel circuitry like MIMOSA-22THRb1 (pre-amp + CDS) (modified pre-amp input T) � end of column discriminators � read-out time ≃ 3.2 µs • MIMOSA-34b chip : � Goal : optimise pixel charge collection system � ∼ 30 different pixels grouped in sub-arrays of 16 × 64 pixels � large pixels only: 33 × 44/55/66 µm 2 40 × 44/55/66 µm 2 & � various sensing node geometries : CCE vs pixel noise ⇛ SNR � few pixels with AC coupling 7

SUMMARY • Engineering run submitted aiming at : � validation of ∼ full chain of MISTRAL � validation of ∼ full chain of ASTRAL � optimisation of in-pixel circuitry � validation of large pixel variants of ASTRAL & MISTRAL � investigation of in-pixel circuitry design adapted to pads over pixels � assessing SEE sensitivity expecting first lab test results in June ⇛ beam tests foreseen in Octobre 2014 • Next step : � AROM version compatible with on-pixel pads � Shuttle of May 12th ? • Final 2014 objective : complete sensor composed of 3 multiplexed FSBB-A units 8

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.