SSD electronics review M. LeVine BNL M.J. LeVine SSD electronics - PowerPoint PPT Presentation

ST STAR AR SSD electronics review M. LeVine BNL M.J. LeVine SSD electronics review, June 20, 2012 1 ST STAR AR Quick overview of upgrade M.J. LeVine SSD electronics review, June 20, 2012 2 SSD ladder ST STAR AR 16 M.J.

ST STAR AR � SSD electronics review M. LeVine BNL M.J. LeVine SSD electronics review, June 20, 2012 1

ST STAR AR � Quick overview of upgrade M.J. LeVine SSD electronics review, June 20, 2012 2

SSD ladder ST STAR AR � 16 M.J. LeVine SSD electronics review, June 20, 2012 3

Previous readout configuration ST STAR AR � M.J. LeVine SSD electronics review, June 20, 2012 4

Readout upgrade concept ST STAR AR � • Reading out front end: – Replace single ADC with 16 ADCs • digitize 16 modules in parallel 2.5 ms -> 163 µ s – Increase sampling rate to 5.00 MHz – All ladders processed concurrently • Transferring data to PC – Increase link throughput to DAQ PC to 120 Mbyte/s per 5 ladders • 1850 µ s -> 450 µ s – Multiple (derandomizing) buffers effectively hides this time • Dead time: 10%@750Hz, <2%@100Hz • [ cf . existing: >80%@750Hz,30% @ 100Hz] M.J. LeVine SSD electronics review, June 20, 2012 5

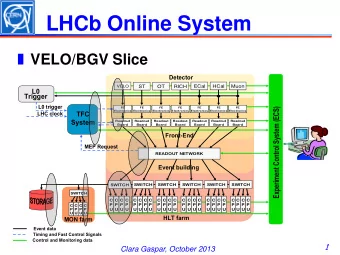

Readout components ST STAR AR � Ladder cards RDO (1 of 8) VME VME interface Slave FPGA FPGA Fiber links Slave FPGA DAQ interface DAQ PC Slave Master FPGA DDL FPGA Slave TRG interface FPGA Slave FPGA South platform Outer support DAQ room VME crate cone M.J. LeVine SSD electronics review, June 20, 2012 6

Data formats ST STAR AR � non zero-suppressed – 3 10-bit ADC values to a 32-bit word – Fixed order: position in buffer/word -> geographical position of strip zero suppressed – Only strips with ADC value above threshold are present – ADC value (10 bits) + strip location (14 bits) – One strip per 32-bit word – Alleviates large memory access burden on DAQ PC – Doing this in real time in FPGA is simple M.J. LeVine SSD electronics review, June 20, 2012 7

AR � Dead time calculation - no zero suppression ST STAR M.J. LeVine SSD electronics review, June 20, 2012 8

Dead time calculations – zero suppression ST STAR AR � 3 % occupancy M.J. LeVine SSD electronics review, June 20, 2012 9

Ladder data path ST STAR AR � 5 MHz 80 MHz module 16 bit width adc 12bit 32 words deep 16 bit serial output packer 16 20 X16 FIFO serializer to fiber 50 MHz 40 MHz JTAG TDOs 2 80 MHz 5 MHz module Write enable: true on 10 clocks only adc 12bit 16 bit serial output 1 set of adc samples: 10 X 16 bits => repacked into: 2 X 4 X 20 bits M.J. LeVine SSD electronics review, June 20, 2012 10

RDO slave - unpacker ST STAR AR � unpacking 4 20-bit words to 5 16-bit words word 1 JTAG TDOs FIFO1 40 MHz word 2 5 MHz 2 FIFO2 10 50 MHz 50 MHz mux word 3 demux FIFO 20 1:10 deserialize deserialize 10 x16 FIFO3 first wd word 4 x16 16 bit FIFO4 word 5 20 bit M.J. LeVine SSD electronics review, June 20, 2012 11

AR � Slave FPGA – ADC processing ST STAR (no zero suppression) Packing register Pedestal - 1 Buffer 0..3 memory 256X32 bits 10 Subtract/ write ped address + ADC 1 1 multiplex 2 Readout to master FPGA write ped data 3 remainder from unpacker 1 Pedestal Buffer 0..3 - memory 256X32 bits 10 Subtract/ read address + multiplex 2 16 ADC 16 3 mode read address address 8 ÷ 3 14 2 10 10 counter Mode: ADC, 0-767 pedestal, or difference Select: ADC, pedestal only, or max(difference,0) Pedestal write M.J. LeVine SSD electronics review, June 20, 2012 12

ST STAR AR � Prototype ladder card testing M.J. LeVine SSD electronics review, June 20, 2012 13

Ladder board: (inside) ST STAR AR � Flex circuit layer Frame cut loose when board is ready for installation M.J. LeVine SSD electronics review, June 20, 2012 14

Ladder board: (outside) ST STAR AR � Edge connector for debug card M.J. LeVine SSD electronics review, June 20, 2012 15

Debug card (via edge connector) ST STAR AR � Provides: • JTAG header to configure FPGA • JTAG header for slow controls o Both will be provided via fiber • USB access to FPGA Version using FTDI naked chip Version using FTDI plugin module M.J. LeVine SSD electronics review, June 20, 2012 16

USB test results ST STAR AR � Number of devices is 2 pcBufRead[16] = 0x41 ==== Device 0 is Subatech DbgV3n1 ====== pcBufRead[17] = 0x41 Serial # A7U3EQBC pcBufRead[18] = 0xFF pcBufRead[19] = 0xFF 1) sending the following bytes pcBufRead[20] = 0x42 0x41 0x41 0xFF 0xFF 0x42 0x42 0x00 0x00 0x43 0x43 pcBufRead[21] = 0x42 0xFF 0xFF 0x44 0x44 0x44 0x44 pcBufRead[22] = 0x00 pcBufRead[23] = 0x00 2) sending the following bytes pcBufRead[24] = 0x43 0x41 0x41 0xFF 0xFF 0x42 0x42 0x00 0x00 0x43 0x43 pcBufRead[25] = 0x43 0xFF 0xFF 0x44 0x44 0x44 0x44 pcBufRead[26] = 0xFF pcBufRead[27] = 0xFF FT_Read = 32 pcBufRead[28] = 0x44 pcBufRead[0] = 0x41 pcBufRead[29] = 0x44 pcBufRead[1] = 0x41 pcBufRead[30] = 0x44 pcBufRead[2] = 0xFF pcBufRead[31] = 0x44 pcBufRead[3] = 0xFF pcBufRead[4] = 0x42 pcBufRead[5] = 0x42 pcBufRead[6] = 0x00 Closed device A7U3EQBC pcBufRead[7] = 0x00 pcBufRead[8] = 0x43 pcBufRead[9] = 0x43 pcBufRead[10] = 0xFF pcBufRead[11] = 0xFF pcBufRead[12] = 0x44 pcBufRead[13] = 0x44 pcBufRead[14] = 0x44 pcBufRead[15] = 0x44 M.J. LeVine SSD electronics review, June 20, 2012 17

Slow controls JTAG signals ST STAR AR � M.J. LeVine SSD electronics review, June 20, 2012 18

Slow controls – read registers ST STAR AR � reading register 0x01 ROBOCLKS: 0xaa 0xaa 0xaa ✔ ✔ = Register with known content at startup reading register 0x02 STATUS : 0x3e 0x60 0x3f reading register 0x03 CONFIG : 0x00 0x00 reading register 0x04 DAC VALS: 0x0a 0xa9 0x55 ✔ reading register 0x07 HYBRIDS : 0x00 0x00 reading register 0x08 LATCHUP : 0x00 reading register 0x09 RALLUMAG: 0x00 0x00 reading register 0x0b BYPASS : 0x00 0x00 reading register 0x0c VERSION : 0x26 0x01 0x20 0x11 ✔ reading register 0x0e TEMPS : 0x00 0x00 0x00 0x00 0x00 0x00 reading register 0x1b IDENTITE: 0xb7 ✔ M.J. LeVine SSD electronics review, June 20, 2012 19

Ladder response vs clock frequency ST STAR AR � 4.3 MHz 5.0 MHz 6.0 MHz Horiz:100 ns/cm M.J. LeVine SSD electronics review, June 20, 2012 20

Level-shifting for bias side ST STAR AR � DOE HFT Review M.J. LeVine SSD electronics review, June 20, 2012 21

Single event upsets ST STAR AR � • Ionizing radiation causes single bit errors in configuration memory (internal to FPGA) – Change FPGA behavior • Scale from observed error frequency in TOF – Estimate 1 error per 10 minutes in SSD • Must pro-actively detect these errors by running CRC checks while acquiring data – Provided by Altera • Time to reconfigure FPGA: < 1 sec M.J. LeVine SSD electronics review, June 20, 2012 22

Fake static source ST STAR AR � M.J. LeVine SSD electronics review, June 20, 2012 23

Ladder card testing road map ST STAR AR � • Use USB to trigger ADC conversion, gather data • Use “static fake ladder” to provide selectable DC level at each ladder input • Allows verification of basic functionality of analog section • Use “dynamic fake ladder” (in design) to verify ADC timing for each ladder. • Use QRDO (in layout) to verify ladder card functionality up through fiber link DOE HFT Review M.J. LeVine SSD electronics review, June 20, 2012 24

Mapping analog response ST STAR AR � • Software – Python script driving – Multiple .exe (C code) • Time to map response for 1 ADC: 30 sec • Time to map all 16 ADCs: 20 minutes – Disconnect/connect flex cable • Basis for future slow controls software • SC uses JTAG header on debug card – Will be replaced by fiber protocol M.J. LeVine SSD electronics review, June 20, 2012 25

Analog response for all ADCs ST STAR AR � ADCs vs. calculated adc0 adc1 adc2 adc3 adc4 adc5 adc6 adc7 adc8 adc9 adc10 adc11 adc12 adc13 adc14 adc15 calc 768 640 512 384 256 128 0 -1.4 -1.2 -1 -0.8 -0.6 -0.4 -0.2 0 0.2 0.4 0.6 0.8 1 1.2 1.4 M.J. LeVine SSD electronics review, June 20, 2012 26

Analog response ST STAR AR � • Non-linear behavior of N-face not yet understood • Discovered we are sensitive to PS fluctuations via DAC – Will be separately regulated in production version (prototype in test) M.J. LeVine SSD electronics review, June 20, 2012 27

Verification of packing code ST STAR AR � • USB output for ADC data • Install USB spy at output of FIFO External to FPGA USB output USB output 5 MHz 80 MHz module 16 bit width adc 12bit 4 words temp 16 bit serial output register 16 FIFO 20 X16 serializer to fiber 40 MHz 50 MHz JTAG TDOs 2 80 MHz 5 MHz module Write enable: true on 10 clocks adc 12bit only 16 bit serial output M.J. LeVine SSD electronics review, June 20, 2012 28

Ladder packer verification ST STAR AR � • Following 4 slides are identical except for notation showing which bits are to be extracted for each word sent to the FIFO • Lines FIFO[0]…FIFO[7] show the 21-bit word exiting the FIFO • Comparison shows that the packer is functioning correctly M.J. LeVine SSD electronics review, June 20, 2012 29

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.