Speeding things up: Getting sloooower The TLB Memory Exception - PowerPoint PPT Presentation

Speeding things up: Getting sloooower The TLB Memory Exception Every new level of paging no p o CPU reduces the memory overhead for computing yes page # frame # Access the mapping function f but increases the time necessary

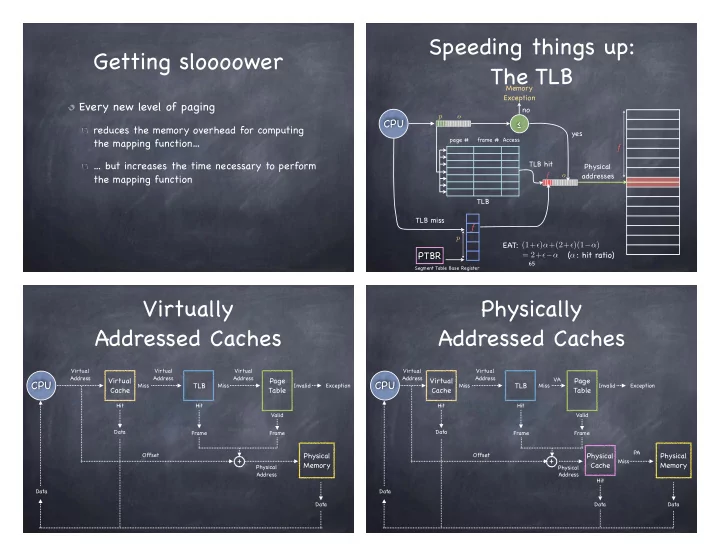

Speeding things up: Getting sloooower The TLB Memory Exception Every new level of paging no p o CPU ≤ reduces the memory overhead for computing yes page # frame # Access the mapping function… f … but increases the time necessary to perform TLB hit Physical addresses the mapping function f o TLB TLB miss f p EAT: (1+ � ) α +(2+ � )(1 − α ) PTBR ( : hit ratio) = 2+ � − α α � 65 Segment Table Base Register Virtually Physically Addressed Caches Addressed Caches Virtual Virtual Virtual Virtual Virtual Address Address Address Address Address Virtual Page Virtual VA Page CPU CPU Miss TLB Miss Invalid Exception Miss TLB Miss Invalid Exception Cache Table Cache Table Hit Hit Hit Hit Valid Valid Data Data Frame Frame Frame Frame PA Offset Physical Offset Physical Physical + + Miss Memory Cache Memory Physical Physical Address Address Hit Data Data Data Data Data

TLB Consistency - I TLB Consistency - I On context switch On context switch VAs of old process should no longer be valid VAs of old process should no longer be valid Change PTBR — but what about the TLB? Change PTBR — but what about the TLB? Option 1: Flush the TLB Option 2: Add pid tag to each TLB entry PID VirtualPage PageFrame Access TLB Entry 1 0x0053 0x0012 R/W Ignore entries with wrong PIDs What if we miss TLB Consistency - II in the TLB? What if OS changes permissions on page? Suppose a 64-bit VAS, with 4KB page and a 512MB physical memory If permissions are reduced, OS must ask Page table has 2 52 entries hardware to purge affected TLB entries At 4 bytes/PTE, Page Table is 16 Petabytes! e.g., on copy-on-write per process! What if permissions are expanded? For Page Table at each level to fit in a single page, each level should span at most 10 bits 6 levels of paging!! But only 2 29 /2 12 = 128K frames…

Page Registers A different approach (a.k.a. Inverted Page Tables) What if mapping size were proportional to For each frame, a register containing the number of frames, not pages? Residence bit is the frame occupied? If PTE = 16 bytes, Page table size = 2MB Page number of the occupying page And since all processes share the same physical Protection bits frames, just one global page table! Searched by page number Inverted page tables Catch? The VAS of different processes may map the same page number to different frames! Basic Inverted Where have all the Page Table Architecture pages gone? Searching 128KB of registers on every memory reference is not fun If the number of frames is small, the page CPU pid p offset f offset Physical registers can be placed in an associative Memory memory---but... } f Large associative memories are expensive search hard to access in a single cycle. pid p consume lots of power Inverted Page Table � 75

Hashed Inverted Demand Paging Page Tables Code pages are stored in a memory-mapped Add a Hash Anchor Table, mapping <pid, VP#> file on disk to an entry of the Inverted Page Table some are currently residing in memory–most are Collisions handled by chaining not pid vpn offset Data and stack pages are also stored in a Index pid vpn next 0 0x1 0x123 memory-mapped file 0x0 1 0xa63 0x184fa 0x184fc OS determines what portion of VAS is hash 0x184fa 0 0x1 ---- mapped in memory 0x184fb 3 0x31ab 0x0a921 0xaf013 physical memory serves as cash for memory- 0x0 mapped file on disk Inverted Hash Anchor Page Table Table 0x184fa 0x123 � 76 � 77 Demand Paging: Allocating a Page Frame Instruction Touches Invalid Mapped Address 1. TLB Miss 8. Disk interrupt when Select “victim” page to evict DMA completes 2. Page Table walk Find all PTEs referring to old page 9. Mark page as valid 3. Page fault (page invalid if page frame was shared 10. Resume process at in Page Table) faulting instruction 4. Exception to kernel Set each PTE to invalid 11. TLB miss 5. Convert VA to file offset Remove any TLB entries 12. Page Table walk – 6. Allocate page frame success! the PTE they are caching is now invalid! (evict page if needed) 13. TLB updated . Initiate disk block read 7 Write changes to page back to disk 14. Execute instruction into page frame

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.