SMD150 Computer Architecture Andrey Kruglyak Lectures 27/3, Lab - PowerPoint PPT Presentation

SMD150 Computer Architecture Andrey Kruglyak Lectures 27/3, Lab preparation Simulation of digital electronic circuits Synchronous Circuit Simulator (SyncSim) MIPS microprocessor Lab assignment 1 3/4, Lab

SMD150 Computer Architecture Andrey Kruglyak

Lectures • 27/3, Lab preparation • Simulation of digital electronic circuits • Synchronous Circuit Simulator (SyncSim) • MIPS microprocessor • Lab assignment 1 • 3/4, Lab preparation • VHDL • Writing VHDL components for SyncSim • Memory module for SyncSim • Lab assignment 2 Andrey Kruglyak, 2007 SMD150 Computer Architecture

Labs • Pre-requisites: • basic understanding of how a microprocessor works • acquaintance with the assembly language • Lab 1, deadline 3/4 • Write (in assembly language) a program for a MIPS simulator • MIPS simulator for SyncSim will be given • Work individually or in pairs Andrey Kruglyak, 2007 SMD150 Computer Architecture

Labs • Lab 2, deadline 21/5§ • Complete a small VHDL tutorial • Design (in VHDL) a model of a super-scalar MIPS processor for SyncSim & test it • Memory module will be given • Work individually or in pairs Andrey Kruglyak, 2007 SMD150 Computer Architecture

ASK QUESTIONS ! • NOW • DURING LABS TODAY AND ON FRIDAY • LATER: andrey.kruglyak@ltu.se Andrey Kruglyak, 2007 SMD150 Computer Architecture

Digital Electronic Circuits • At the lowest level consist of transistors connected by wires • More complex elements are logic gates (AND, OR, XOR, NOT, etc.) and memory elements (buffers and registers) • We will speak about program counter, register file, data/instruction memory, ALUs, ... • We will see examples of different circuits, but work with designs of microprocessors Andrey Kruglyak, 2007 SMD150 Computer Architecture

Testing & Simulation • Digital circuits can be tested (build, send input, check output) • Digital circuit can be simulated in software (send input, observe internal behavior, check output) • Simulation can be performed in different ways, usually by introducing various simplifications • We will concentrate on functional behavior at the register transfer level (RTL) (i.e. producing the correct result) and ignore the timely behavior of the circuits • each clock cycle is treated as one simulation step • hold time, propagation delay, set-up time, etc. are ignored • clock skew is ignored Andrey Kruglyak, 2007 SMD150 Computer Architecture

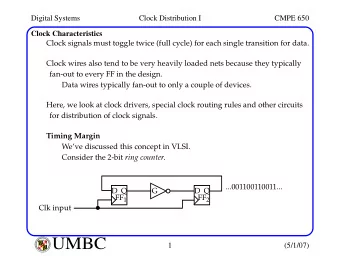

Synchronous Circuits • Practically all digital circuits are synchronous • i.e. there is one clock signal for a system (or a subsystem) 1 0 • the clock is delivered to some components of the system, these are called synchronous components • the clock is delivered to them (almost) simultaneously • the synchronous components change value only at the (rising) edge of the clock depending on the input at that moment, and hold the output constant until the next (rising) edge of the clock • other components change their value as soon as any input changes, and the clock is not delivered to them; these are called combinatorial components Andrey Kruglyak, 2007 SMD150 Computer Architecture

Synchronous Circuits • in one clock cycle, a signal travels from one synchronous component through a number of combinatorial components to another synchronous component • at the (rising) clock edge, all inputs to a synchronous component must be ready to be sampled • the longest path between two synchronous components is known as the critical path • the length of a clock cycle must be larger than the critical path • it is important to avoid combinatorial loops, any combinatorial loop leads to a signal never stabilizing and the output of the circuit becomes unpredictable Andrey Kruglyak, 2007 SMD150 Computer Architecture

SyncSim • The software we will use for simulation has been developed here at LTU • You will use last-year’s version for the first lab, and a newer version for the second lab • SyncSim is a general synchronous circuit simulator • it allows to define any circuit with synchronous and combinatorial components • the components can be defined in Java or in VHDL (according to some strict templates), and later connected into a complete circuit • during simulation the internal state of each component as well as the value in the wires between them can be observed after each clock cycle Andrey Kruglyak, 2007 SMD150 Computer Architecture

SyncSim • Note that defining a circuit and running a simulation are two different tasks! • For a model of a microprocessor, input (instruction memory and (possibly) data memory) must be provided for simulation • Same model can be simulated with various programs (=contents of the instruction memory) • For the first lab, a ready SyncSim model of a simplified MIPS microprocessor will be provided; your task will be to write a program for it • In the second lab, you will build components for a super-scalar MIPS in VHDL and connect them in SyncSim; you will also write programs to test your design Andrey Kruglyak, 2007 SMD150 Computer Architecture

MIPS (lab 1) • MIPS is a large family of microprocessors, produced by MIPS Technologies • It is a RISC (Reduced Instruction Set Computer) processor with 32 registers • It is a 32-bit processor, and each instruction is also 32 bit wide • We will work with a simplified single-cycle version (i.e. no pipelines) • The model we will use for the first lab is written entirely in Java • We will use tools available from MIPS Technologies to compile program code into binary (machine) code Andrey Kruglyak, 2007 SMD150 Computer Architecture

MIPS Model for SyncSim Demo

LAB 1: GOALS • Learn how to use SyncSim • Learn a simplified version of MIPS • Refresh / learn the MIPS assembly language Andrey Kruglyak, 2007 SMD150 Computer Architecture

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.