Sequential Circuits Foundations of Global Networked Computing: - PowerPoint PPT Presentation

IWKS 3300: NAND to Tetris Spring 2019 John K. Bennett Sequential Circuits Foundations of Global Networked Computing: Building a Modern Computer From First Principles This course is based upon the work of Noam Nisan and Shimon Schocken. More

IWKS 3300: NAND to Tetris Spring 2019 John K. Bennett Sequential Circuits Foundations of Global Networked Computing: Building a Modern Computer From First Principles This course is based upon the work of Noam Nisan and Shimon Schocken. More information can be found at (www.nand2tetris.org).

First, some follow- up from last time…

Demonstrating the Book’s ALU x=0 x=!x y=0 y=!y +/ AND out = !out if out = 0, zr = 1 if out < 0, ng = 1

The Book’s ALU

4:1 Multiplexor as a Function Generator A-D are the Function Select S0 and S1 are the Variables

4:1 Multiplexor as a Function Generator A B C D Function 0 0 0 0 0 S0 • S1 0 0 0 1 S0 • !S1 0 0 1 0 0 0 1 1 S0 !S0 • S1 0 1 0 0 0 1 0 1 S1 0 1 1 0 S0 XOR S1 0 1 1 1 S0 + S1 !S0 • !S1 1 0 0 0 1 0 0 1 !(S0 XOR S1) 1 0 1 0 !S1 1 0 1 1 S0 + !S1 1 1 0 0 !S0 1 1 0 1 !S0 + S1 1 1 1 0 !S0 + !S1 1 1 1 1 1

Programmable Logic

Programmable Logic Example 16R4 PAL

Field Programmable Gate Array (FPGA)

FPGA Logic Arrays (simple and complex)

FPGA Special Cells Soft (e.g., MicroBlaze) and hard (e.g., PowerPC) processors Special pre- configured cells

Metal Oxide Transistor

Building Gates on Silicon NAND By Reza Mirhosseini - originally uploaded to en.wikipedia

Building Gates on Silicon 5 x 2:1 Multiplexor

Now, back to sequential circuits…

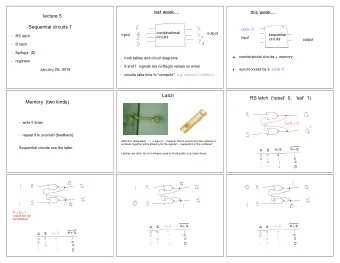

Sequential VS Combinatorial Circuits Combinatorial devices: outputs are a function of inputs only – input changes will propagate to the output after a finite (usually small) propagation delay. Sequential devices: outputs are a function of both inputs and current state – inputs and current state are periodically sampled and new outputs are computed. Sequential devices are sometimes called “clocked devices,” because the period sampling is typically initiated by a “clock” signal, like a square wave: The low-level behavior of sequential circuits, particularly circuits that employ feedback, can be complex to analyze and design. The good news: In the Hack computer, all sequential chips are based upon a single low-level sequential gate, called a “D flip flop”, or DFF Clock-dependency details are encapsulated at the DFF level ( almost ) Higher-level sequential chips are built on top of DFF gates using combinatorial logic only.

Sequential VS combinational logic Best to not have combinatorial logic on both sides. The Book’s HDL simulator is OK with this; LogicCircuit less so. Why? Combinational chip Sequential chip (optional) time delay (optional) comb. DFF comb. comb. in out in out logic gate(s) logic logic out = some function of (in) out(t) = some function of (in(t-1), out(t-1))

Basic S-R Flip Flop (no clock)

The Clock tock tock tock tock tick tick tick tick clock signal cycle cycle cycle cycle In Hack jargon, a clock cycle = tick -phase (low), followed by a tock -phase (high) In real hardware, the clock is implemented by an oscillator (a special circuit that, well, oscillates) In the Hack hardware simulator, clock cycles can be simulated either Manually, by the user, or “Automatically,” by a test script.

Implementing a Crystal Oscillator with NAND Gates Practical Note: Design for 2x desired frequency and divide by 2; (Xtal oscillators have accurate frequency, but asymmetric period)

Implementing a Divide by Two

The Book’s D Flip -flop in DFF out out(t) = in(t-1) A fundamental state-keeping device The book assumes that the DFF implementation is magic, but in fact it can be readily implemented using NAND gates. In the Hack computer, memory devices are made from numerous flip-flops, all regulated by the same master clock signal Notational convention (we sometimes omit the “CLK”) : sequential = sequential in in out out chip chip (notation) clock signal

Two Ways to Implement the Book’s D Flip -flop: 1 in DFF out out(t) = in(t-1)

Two Ways to Implement the Book’s D Flip -flop: 2 in DFF out out(t) = in(t-1)

You Do Not Have to Implement the Book’s D Flip -flop (unless you want to simulate inside LogicCircuit) Just download (or create) the Nand and DFF templates in DFF out out(t) = in(t-1)

A Real D Flip Flop With Asynchronous Set’ and Reset’

Flip Flops in the Real World The critical design parameters for Metastability: What happens if Tsu or Th are violated a flip flop are setup and hold times, and propagation delay. Setup : The length of time before the clock edge that inputs must be stable ( Tsu ) Hold Time : The length of time after the clock edge that inputs must be stable ( Th ) Fmax Example: 74F74 Propagation Delay : The time it Tsu = 3ns (from data sheet) takes for outputs to become stable after the clock edge ( Pd ) Th = 1ns (from data sheet) Pd = 9ns (from data sheet) Maximum Frequency can be Fmax = 1/(12ns) = 83 MHz calculated: Fmax = 1 / (Pd + Tsu) This is a worst case example

D Flip Flop With Asynchronous Set’ and Reset’ From NANDs Q CLK Q- ½ of 74x74

Divide By Two Circuit (book’s simulator will not accept this) Q Q- CLK D

Implementing Edge Triggering (74x74 is edge triggered)

Q: Are there other kinds of FF’s? A: Yes Some others: We have covered: JK FF SR (NAND) FF D FF with sync S&R D (NAND) FF Toggle FF D (NAND) with async. S&R SR NOR FF Positive-edge-triggered D FF SR AND-OR FF Gated SR FF Earle latch Master – slave D FF T FF Gated versions of all of these

What’s a JK Flip Flop?

JK Flip Flops Require Care in Design

Who invented the JK Flip Flop? a. Jack Kilby (what some think) b. Edward Nelson (what others think) c. We don’t know Answer: I’m going to go with (c.). Here’s why: Jack Kilby introduction at Rice University in 1973 “He has been 1. credited with the invention of the JK flip flop.” Lot’s of web sites state that Kilby invented JK FFs. Kilby himself never made this claim. But he did win a Nobel Prize in Physics for invention of the integrated circuit. Kilby started at TI in 1958, and JK FF’s are mentioned in a 1953 2. patent (US 2,850,566) by Edward C. Nelson. Some web sites use this datum to assert that Nelson invented JK FFs. 3. But Nelson does not claim invention of JK FFs in the patent.

What’s in a Patent? 1. Specification – invention background and description 2. Claims – what is unique about the invention Nelson’s Patent: “HIGH - SPEED PRINTING SYSTEM” In the Specification: “…Each flip -flop or bistable multivibrator includes two input terminals, hereinafter termed the j-input and the k-input terminals, respectively, and two output terminals for producing complementary bi-valued electrical output signals hereinafter termed Q and Q, respectively. Signals applied separately to the j-input and k-input terminals set the flip-flop to conduction states corresponding to the binary values one and zero, respectively, while signals applied simultaneously to both input terminals trigger or change the conduction state of the flip- flop…” Flip-flops are not mentioned in the claims, which all relate to printing. “What is claimed as new is: 1. A high-speed printing system for printing on a printing medium a line of intelligence information …”

The JK Flip-Flop was Patented in 1969 (filed in 1966) Miller did not disclose Nelson’s patent to the examiner. Miller’s patent is likely invalid due to obviousness and prior art.

JKB’s Best Guess The JK Flip Flop was likely invented sometime in the early days of vacuum tube computing by an engineer who was too busy getting things done to worry about patents. The idea probably became common knowledge to digital designers by the early 1950’s. …Miller’s patent should have probably never issued. We now return to your regularly scheduled programming…

1- bit register (the book calls it “Bit”) load Objective: build a storage unit that can: (a) Change its state to a given input out in Bit (b) Maintain its state over time (until changed) if load(t-1) then out(t)=in(t-1) else out(t)=out(t-1) out in in out DFF DFF out(t) = in(t-1) Basic building block out(t) = out(t-1) ? out(t) = in(t-1) ? The book, and the book’s simulator prohibit such feedback, but in practice, feedback can be very useful, e.g., div-by-2., although you cannot tie two normal outputs together.

Bit register (cont.) Interface Implementation load load in out out in Bit MUX DFF if load(t-1) then out(t)=in(t-1) else out(t)=out(t-1) o Load bit o Read logic o Write logic

Bit Register Implementation Implementation load in out MUX DFF

Better Bit Register Implementation A Bit from DFF (red circle) and 2:1 mux (green circle) Logical Design load in out MUX DFF

Multi-bit register load load . . . out in Bit out in Bit Bit Bit w w if load(t-1) then out(t)=in(t-1) if load(t-1) then out(t)=in(t-1) else out(t)=out(t-1) else out(t)=out(t-1) 1-bit register w-bit register o Register’s width: a trivial parameter o Read logic o Write logic

Multi-Bit (16 bit) Register

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.