Reversible Logic Synthesis of k Input, m Output Lookup Tables - PowerPoint PPT Presentation

Reversible Logic Synthesis of k Input, m Output Lookup Tables Alireza Shafaei, Mehdi Saeedi, Massoud Pedram University of Southern California Department of Electrical Engineering Supported by the IARPA Quantum Computer Science Outline

Reversible Logic Synthesis of k ‐ Input, m ‐ Output Lookup Tables Alireza Shafaei, Mehdi Saeedi, Massoud Pedram University of Southern California Department of Electrical Engineering Supported by the IARPA Quantum Computer Science

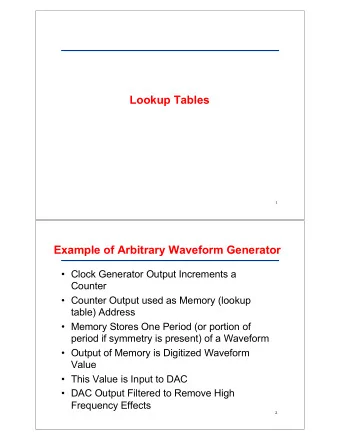

Outline • Introduction • Lookup Tables (LUT) – Quantum Walk on Binary Welded Tree • Related Work • Proposed Synthesis Algorithm • Simulation Results • Conclusion Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 1 Department of Electrical Engineering, University of Southern California

Quantum Circuits • Data is carried out by quantum bits or qubits • Quantum gates � – Unitary matrix ( ) – Reversible • Multiple ‐ Control Toffoli (MCT) gate – Negative Control x x Control lines – Positive Control y y remain unchanged z z w’ if (x=0 & y=1 & z=1) w o w w otherwise Target line � � � � � � � �� Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 2 Department of Electrical Engineering, University of Southern California

Reversible Logic Synthesis • Quantum algorithms – Quantum part, e.g., Quantum Fourier Transform – Classical part, or Oracles • Reversible synthesis methods • General purpose vs. special purpose synthesis • Automatic synthesis of a specific type of quantum circuits – Quantum walk on binary welded tree – Modular exponentiation circuits Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 3 Department of Electrical Engineering, University of Southern California

Quantum Walk on Binary Welded Tree • Random movement on a Binary Welded Tree (BWT) • Oracle [1] : V c (a) = b Color c Node a Node b a b 7 16 8 17 9 15 11 19 12 22 For black edges 13 18 [1] A. M. Childs et al ., “Exponential algorithmic speedup by a quantum walk,” in Proc. of the 35th Annual ACM Symposium 14 20 on Theory of Computing , pp. 59–68, 2003. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 4 Department of Electrical Engineering, University of Southern California

LUT Synthesis Look ‐ Up Table (LUT) • read ‐ only inputs – zero ‐ initialized outputs – 16 = (10000) 2 • LUT realization with MCT gates x 0 – e.g., 16 7 x 0 x y x 4 x 4 16 7 0 y 0 0 y 0 x 4 x 3 x 2 x 1 x 0 y 4 y 3 y 2 y 1 y 0 0 0 10000 00111 0 0 0 0 7 = (00111) 2 0 y 4 0 y 4 Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 5 Department of Electrical Engineering, University of Southern California

Oracle Implementation • Straightforward implement the oracle for black edges a y 7 16 8 17 – High cost 9 15 11 19 12 22 7 16 16 7 13 18 14 20 Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 6 Department of Electrical Engineering, University of Southern California

Related Work • ESOP ‐ based methods [2] � output, �� a minterm of � – � �� �� �� – – Use an ESOP minimizer to minimize � • General ‐ purpose reversible synthesis methods [3] – Copying input registers into output registers – Apply synthesis algorithm on output register [2] K. Fazel, M. Thornton, and J. Rice, “ESOP ‐ based Toffoli gate cascade generation,” in PACRIM , pp. 206 –209, Aug. 2007. [3] M. Saeedi and I. L. Markov, “Synthesis and optimization of reversible circuits ‐ a survey,” ACM Computing Surveys , arXiv:1110.2574, 2013. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 7 Department of Electrical Engineering, University of Southern California

Proposed Synthesis Algorithm • Cube sharing [4] – To reduce the number of MCT gates • Cofactor sharing – To reduce the number of control lines • Un ‐ computation – To reuse the ancilla line • Look ‐ ahead search – To improve the quality of results [4] N. M. Nayeem and J. E. Rice, “A shared ‐ cube approach to ESOP ‐ based synthesis of reversible logic,” in Facta universitatis ‐ series: Electronics and Energetics , vol. 24, no. 3, pp. 385–402, Dec. 2011. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 8 Department of Electrical Engineering, University of Southern California

Cube Sharing • Reduces the number of MCT gates y 0 = c 1 +abc y 0 = c 1 +abc y 1 = abc y 1 = c 2 +abc c 1 +c 2 No cube sharing Zero ‐ initialized ancilla available c 2 +abc +: modulo 2 addition c 1 +c 2 +c 2 +abc =c 1 +abc Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 9 Department of Electrical Engineering, University of Southern California

Cofactor Sharing • Reduces the number of control lines y 0 = ab ab is the shared cofactor, which is also a cube for y 0 y 1 = abc Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 10 Department of Electrical Engineering, University of Southern California

Un ‐ computation Ancilla reuse • y 0 = abc ab is the shared cofactor, but does not appear on y 1 = abd neither of the outputs Zero ‐ initialized ancilla available Un ‐ computation of ab Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 11 Department of Electrical Engineering, University of Southern California

Example • 3 ‐ input, 6 ‐ output LUT Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 12 Department of Electrical Engineering, University of Southern California

Example: Lists cube_list input to the synthesis algorithm shared_cofactor_list constructed by pair ‐ wise comparison of cubes Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 13 Department of Electrical Engineering, University of Southern California

Synthesis • Pick a shared cofactor, implement it along with all its dependent cubes • Which shared cofactor to choose first? S 1 S 2 S 3 If we choose S 1 , then C 1 , C 2 , and C 3 will be created C 1 C 2 C 3 C 4 C 5 C 6 S 2 S 3 After removing S 1 , C 1 , C 2 , and C 3 , S 2 is no more a shared cofactor C 4 C 5 C 6 S i : shared cofactors, C i : cubes Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 14 Department of Electrical Engineering, University of Southern California

Look ‐ ahead Search • Exhaustive search until depth d • Find path p with the lowest cost • Pick the first node (from top) in p as the shared cofactor Level ‐ 0 shared cofactors look ‐ ahead depth Remaining shared cofactors at Level ‐ i Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 15 Department of Electrical Engineering, University of Southern California

Synthesis Algorithm look ‐ ahead search synthesis Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 16 Department of Electrical Engineering, University of Southern California

Simulation Setup • Implemented in C++ • EXORCISM ‐ 4 [5] to initially construct a minimized ESOP representation • At most one ancilla in all circuits • 3 ‐ level of look ‐ ahead ( d = 3 ) • Intel Core i7 ‐ 2600, 8GB memory [5] A. Mishchenko and M. Perkowski, “Fast heuristic minimization of exclusive sum ‐ of ‐ products,” in Reed ‐ Muller Workshop , 2001. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 17 Department of Electrical Engineering, University of Southern California

Results: MCNC Benchmarks • 28% (on average ) improvement over [13] – Runtime from a few seconds to about 5 minutes [13] N. M. Nayeem and J. E. Rice, “A shared ‐ cube approach to ESOP ‐ based synthesis of reversible logic,” in Facta universitatis ‐ series: Electronics and Energetics , vol. 24, no. 3, pp. 385–402, Dec. 2011. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 18 Department of Electrical Engineering, University of Southern California

Results: Modular Exponentiation (1) • 52% (on average ) improvement over [7, Table 8] – Runtime less than one minute in our method – (# of Toffoli, # of CNOT, cost) [7] I. L. Markov and M. Saeedi, “Constant ‐ optimized quantum circuits for modular multiplication and exponentiation,” QIC ., vol. 12, no. 5 ‐ 6, pp. 361– 394, May 2012. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 19 Department of Electrical Engineering, University of Southern California

Results: Modular Exponentiation (2) [7] I. L. Markov and M. Saeedi, “Constant ‐ optimized quantum circuits for modular multiplication and exponentiation,” QIC ., vol. 12, no. 5 ‐ 6, pp. 361– 394, May 2012. Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 20 Department of Electrical Engineering, University of Southern California

Sample Circuit • (4, 7) ‐ LUT in modular exponentiation for M = 65 Can be removed by a post ‐ synthesis optimization process Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 21 Department of Electrical Engineering, University of Southern California

Conclusion • A synthesis algorithm for LUT’s by reversible gates – Cofactor Sharing – Un ‐ computation – Look ‐ ahead Search • Improvement of synthesis cost – 52% on average in modular exponentiation algorithm – 28% on average on the MCNC benchmarks Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 22 Department of Electrical Engineering, University of Southern California

Thank you! Alireza Shafaei, Mehdi Saeedi, Massoud Pedram 17 ‐ Mar ‐ 13 23 Department of Electrical Engineering, University of Southern California

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.