PyMTL/Pydgin Tutorial Schedule 8:30am 8:50am Virtual Machine - PowerPoint PPT Presentation

Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit PyMTL/Pydgin Tutorial Schedule 8:30am 8:50am Virtual Machine

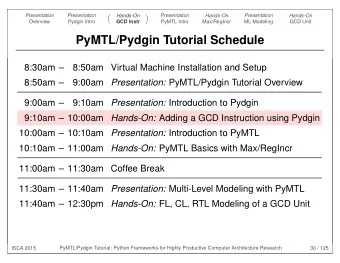

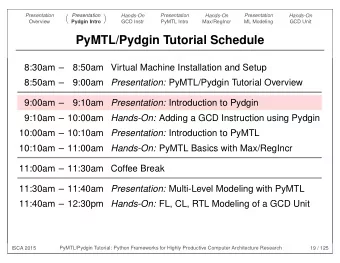

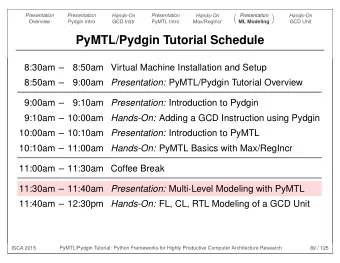

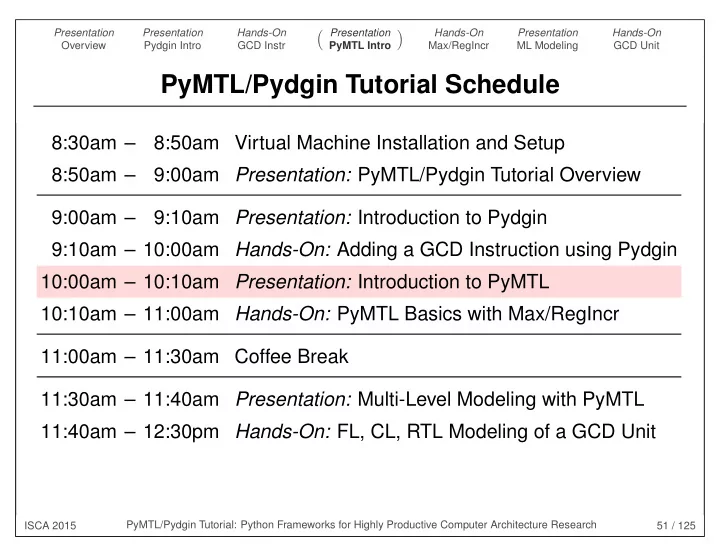

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit PyMTL/Pydgin Tutorial Schedule 8:30am – 8:50am Virtual Machine Installation and Setup 8:50am – 9:00am Presentation: PyMTL/Pydgin Tutorial Overview 9:00am – 9:10am Presentation: Introduction to Pydgin 9:10am – 10:00am Hands-On: Adding a GCD Instruction using Pydgin 10:00am – 10:10am Presentation: Introduction to PyMTL 10:10am – 11:00am Hands-On: PyMTL Basics with Max/RegIncr 11:00am – 11:30am Coffee Break 11:30am – 11:40am Presentation: Multi-Level Modeling with PyMTL 11:40am – 12:30pm Hands-On: FL, CL, RTL Modeling of a GCD Unit PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 51 / 125

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit Computer Architecture Research Abstractions ApplicaBons! Algorithms! Compilers! Industry& Academic& Development& Research& InstrucBon!Set!Architecture! & & Hundreds!of! A!Few!! Microarchitecture! Engineers! Researchers! VLSI! Sea!of!Transistors! PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 52 / 125

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit Computer Architecture Research Methodologies FuncBonal!Level! Greater&& Algorithm&and&ISA& Simula>on& Development& Speed& Cycle!Level! Modeling&Towards&Layout Design&Space& Explora>on& Register!Transfer!Level! Greater&& Model& Area/Energy/Timing&Valida>on& Detail& and& Prototype&Development& PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 53 / 125

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit Computer Architecture Research Toolflows FuncBonal!Level! Different!languages,!! paKerns,!and!tools! Algorithm&and&ISA& Development& Cycle!Level! The&Computer&Architecture& Design&Space& Research&Methodology&Gap Explora>on& Register!Transfer!Level! Area/Energy/Timing&Valida>on& and& Prototype&Development& PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 54 / 125

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit Great Ideas From Prior Frameworks • ConcurrentUStructural&Modeling ! Consistent!interfaces!across!abstracBons! (Liberty,!Cascade,!SystemC) " ! " ! • Unified&Modeling&Languages& Unified!design!environment!for!FL,!CL,!RTL! (SystemC)! ! ! ! • Hardware&Genera>on&Languages& ProducBve!RTL!design!space!exploraBon! (Chisel,!Genesis2,!BlueSpec,!MyHDL)! ! ! ! • HDLUIntegrated&Simula>on&Frameworks& ProducBve!RTL!validaBon!and!cosimulaBon! (Cascade) " ! " ! • LatencyUInsensi>ve&Interfaces& Component!and!test!bench!reuse! (Liberty,!BlueSpec) & PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 55 / 125

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit What is PyMTL? ! • A!Python!EDSL!for!concurrentNstructural!hardware!modeling! • A!Python!API!for!analyzing!models!described!in!the!PyMTL!EDSL!! • A!Python!tool!for!simulaBng!PyMTL!FL,!CL,!and!RTL!models! • A!Python!tool!for!translaBng!PyMTL!RTL!models!into!Verilog! • A!Python!tesBng!framework!for!model!validaBon! ! TesBng!Framework! Model!EDSL! SimulaBon! ! Tool! API! TranslaBon! Tool! PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 56 / 125

⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit The PyMTL Framework Model&/&Tool&Split& Specifica>on& Tools& Output! Test!&!Sim! SimulaBon! Traces!&! Harness! Tool! VCD! Model! TranslaBon! EDA! Model! Elaborator! Verilog! Instance! Tool! Toolflow! User! User!Tool! Config! Tool! Output! FPGA! High!Level! StaBc! Dynamic! VisualizaBon! Analysis! Checking! SimulaBon! Synthesis! PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 57 / 125

! ⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit PyMTL 101: Traditional Model in Python def max_unit( input_list ): ! f(x)! return max( input_list ) ! [!3,!1,!2,!0!]! 3!! PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 58 / 125

! ! ! ! ⇣ Presentation Presentation Presentation Hands-On Hands-On Presentation Hands-On ⌘ Overview Pydgin Intro GCD Instr PyMTL Intro Max/RegIncr ML Modeling GCD Unit PyMTL 101: Model in PyMTL Embedded DSL def max_unit( input_list ): ! f(x)! return max( input_list ) ! [!3,!1,!2,!0!]! 3!! class MaxUnitFL( Model ): ! def __init__( s, nbits, nports ): ! s.in_ = InPort[nports]( nbits ) ! f(x)& s.out = OutPort( nbits ) ! @s.tick_fl ! def logic(): ! s.out.next = max( s.in_ ) ! PyMTL/Pydgin Tutorial: Python Frameworks for Highly Productive Computer Architecture Research ISCA 2015 59 / 125

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.