Problems with physical addressing CS 251 Fall 2019 CS 240 - PowerPoint PPT Presentation

Problems with physical addressing CS 251 Fall 2019 CS 240 Principles of Programming Languages Foundations of Computer Systems Ben Wood Main memory 0: 1: Physical address 2: 3: (PA) Virtual Memory CPU 4: 4 5: 6: 7: Process

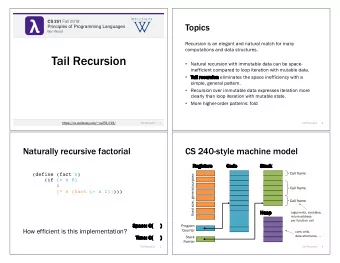

λ Problems with physical addressing CS 251 Fall 2019 CS 240 Principles of Programming Languages Foundations of Computer Systems Ben Wood Main memory 0: 1: Physical address 2: 3: (PA) Virtual Memory CPU 4: 4 5: 6: 7: Process Abstraction, Part 2: Private Address Space 8: ... M-1: Motivation : why not direct physical memory access? Address translation with pages Optimizing translation : translation lookaside buffer Data Extra benefits : sharing and protection Memory as a contiguous array of bytes is a lie! Why? https://cs.wellesley.edu/~cs240/ Virtual Memory 1 Virtual Memory 2 Problem 1: memory management Problem 2: capacity 64-bit addresses can address Physical main memory offers Main memory several exabytes a few gigabytes (18,446,744,073,709,551,616 bytes) (e.g. 8,589,934,592 bytes) Process 1 stack × Process 2 ? heap What goes (To scale with 64-bit address space, Process 3 you can't see it.) where? code … globals Process n … Also: Context switches must swap out entire memory contents. 1 virtual address space per process, Isn't that expensive ? with many processes… Virtual Memory 3 Virtual Memory 4

Problem 3: protection Solution: Virtual Memory (address indirection ) data Virtual address space Physical main memory Process i Process 1 virtual Physical memory addresses Process j virtual-to-physical mapping physical Virtual address space addresses Problem 4: sharing Physical main memory Process n virtual Process i addresses data Single physical address space Private virtual address Process j space per process. managed by OS/hardware. Virtual Memory 5 Virtual Memory 6 Indirection Tangent: i ndirection everywhere "2" (it's everywhere!) 0 • Pointers 1 Direct naming "2" • Constants Thing 2 "2" • Procedural abstraction 3 What X 4 currently "x" • Domain Name Service (DNS) maps to 5 • Dynamic Host Configuration Protocol (DHCP) Indirect naming 2 6 "x" "x" 7 • Phone numbers "x" • 911 What if we move Thing ? • Call centers • Snail mail forwarding “Any problem in computer science can be solved by adding another level of indirection.” • … –David Wheeler, inventor of the subroutine, or Butler Lampson Another Wheeler quote? "Compatibility means deliberately repeating other people's mistakes." Virtual Memory 7 Virtual Memory 8

Page-based mapping Virtual addressing and address translation fixed-size, aligned pages page size = power of two Virtual Memory Management Unit Address Space translates virtual address to physical address 0 Virtual Main memory Physical Page Address Space 0: 0 0 CPU Chip 1: Physical Virtual 2: Page Virtual address Physical address Page 3: 0 (VA) (PA) 1 CPU MMU 4: Physical 4 Virtual 4100 5: Page Page 6: 1 2 7: … Virtual 8: Map virtual pages Page ... … 3 onto physical pages. Physical M-1: Page 2 p - 1 2 m - 1 Virtual Data Page 2 v - 1 2 n - 1 Some virtual pages do not fit! Where are they stored? Physical addresses are invisible to programs. Virtual Memory 9 Virtual Memory 10 Not drawn to scale Virtual memory: cache for disk? Cannot fit all virtual pages! Where are the rest stored? Virtual Memory virtual address space Address Space usually much larger than DRAM SRAM 0 physical address space Virtual Physical Memory ~4 MB ~8 GB ~500 GB Page Address Space 0 0 L1 Physical Virtual I-cache Page Page L2 Disk Main 0 1 unified 32 KB Memory Physical Virtual cache Page L1 Page CPU Reg 1 D-cache 2 … Virtual Throughput: 16 B/cycle 8 B/cycle 2 B/cycle 1 B/30 cycles Page solid-state "flash" … 3 Latency: 3 cycles 14 cycles 100 cycles millions 1. On disk if used or Physical spinning Page 2 p - 1 magnetic platter. 2 m - 1 Virtual Cache miss penalty Page (latency): 33x 2. Nowhere if not (yet?) used 2 v - 1 2 n - 1 Memory miss penalty (latency): 10,000x Example system Virtual Memory 11 Virtual Memory 12

Design for a slow disk: exploit locality Design for a slow disk: exploit locality Virtual Memory Virtual Memory Large page size Page size? Address Space Address Space usually 4KB, up to 2-4MB 0 0 Virtual Virtual Physical Memory Physical Memory Page Page Address Space Address Space 0 0 0 0 Physical Physical Virtual Virtual Page Page Page Page Fully associative 0 0 1 1 Associativity? Physical • Store any virtual page in any physical page Physical Virtual Virtual Page Page • Large mapping function Page Page 1 1 2 2 … … Virtual Virtual Page Page … … 3 3 on disk on disk Physical Physical Page Page 2 p - 1 2 p - 1 2 m - 1 2 m - 1 Virtual Virtual Sophisticated Replacement Page Page 2 v - 1 2 v - 1 replacement policy policy? 2 n - 1 2 n - 1 Write Write-back • Not just hardware policy? Virtual Memory 13 Virtual Memory 14 Address translation Page table Physical pages array of page table entries (PTEs) (Physical memory) mapping virtual page to where it is stored Main memory VP 1 PP 0 Physical Page Number 0: Valid or disk address VP 2 CPU Chip 1: Virtual address Physical address 2: PTE 0 0 null 3: VP 7 (VA) (PA) 1 CPU MMU 4: 4 1 4100 5: VP 4 PP 3 6: 0 7: 1 8: 0 null ... 0 M-1: PTE 7 1 Swap space page table (Disk) Data VP 3 Memory resident, VP 6 managed by HW (MMU), OS How many page tables are in the system? Virtual Memory 15 Virtual Memory 16

Address translation with a page table Page hit: virtual page is in memory Physical pages (Physical memory) Virtual Page Number VP 1 PP 0 Virtual address (VA) Page table Physical Page Number base register Virtual page number (VPN) Virtual page offset (VPO) Valid or disk address VP 2 (PTBR) PTE 0 0 null Base address Page table VP 7 1 PP 0 of current process's page table 1 PP 1 Valid Physical page number (PPN) VP 4 PP 3 0 On disk 1 PP 3 0 null 0 On disk PTE 7 1 PP 2 Swap space Virtual page mapped page table (Disk) to physical page? yes = page hit VP 3 Physical page number (PPN) Physical page offset (PPO) VP 6 Physical addres s (PA) Virtual Memory 17 Virtual Memory 18 Page fault: Page fault: exceptional control flow Physical pages (Physical memory) Virtual Page Number Process accessed virtual address in a page that is not in physical memory. VP 1 PP 0 Physical Page Number Valid or disk address VP 2 PP 1 Process PTE 0 0 null VP 7 PP 2 User Code OS exception handler 1 PP 0 1 PP 1 VP 4 PP 3 0 On disk exception: page fault 1 PP 3 movl 0 null Load page 0 On disk into memory PTE 7 1 PP 2 return Swap space page table (Disk) VP 3 VP 6 Returns to faulting instruction: movl is executed again ! Virtual Memory 19 Virtual Memory 20

"Page out" Page fault: 1. page not in memory Page fault: 2. OS evicts another page. Physical pages Physical pages (Physical memory) (Physical memory) Exception! Virtual Page Number Virtual Page Number VP 1 PP 0 VP 1 PP 0 Physical Page Number Physical Page Number Valid or disk address Valid or disk address VP 2 VP 2 PTE 0 0 null PTE 0 0 null VP 7 VP 7 1 PP 0 0 On disk 1 PP 1 1 PP 1 VP 4 VP 4 PP 3 PP 3 0 On disk 0 On disk 1 PP 3 1 PP 3 0 null 0 null 0 On disk 0 On disk PTE 7 1 PP 2 PTE 7 1 PP 2 Swap space Swap space page table (Disk) page table (Disk) VP 3 VP 3 What now? VP 6 VP 6 OS handles fault VP 1 Virtual Memory 21 Virtual Memory 22 "Page in" Page fault: 3. OS loads needed page. Terminology Physical pages (Physical memory) Virtual Page Number context switch VP 3 PP 0 Physical Page Number Switch control between processes on the same CPU. Valid or disk address VP 2 page in PTE 0 0 null VP 7 Move page of virtual memory from disk to physical memory. 1 On disk 1 PP 1 page out VP 4 PP 3 1 PP 0 Move page of virtual memory from physical memory to disk. 1 PP 3 0 null thrash 0 On disk Total working set size of processes is larger than physical memory. PTE 7 1 PP 2 Swap space Most time is spent paging in and out instead of doing useful work. page table (Disk) VP 3 Finally: VP 6 Re-execute faulting instruction. Page hit! VP 1 Virtual Memory 23 Virtual Memory 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.