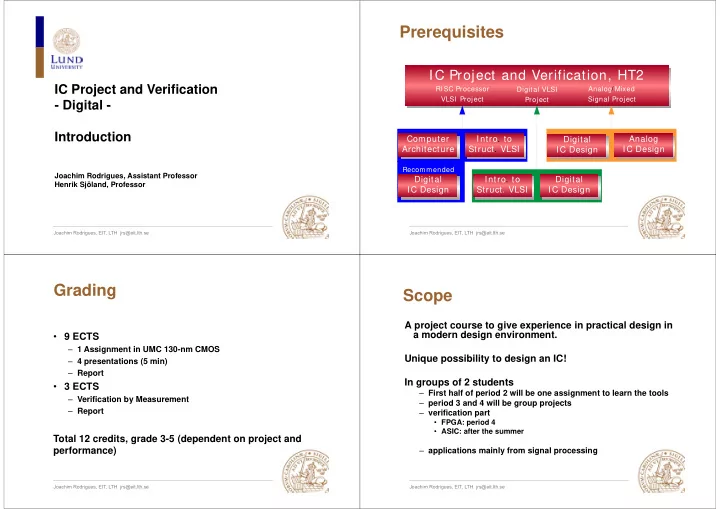

Prerequisites IC Project and Verification, HT2 IC Project and Verification RISC Processor Analog/ Mixed Digital VLSI VLSI Project Signal Project Project - Digital - Introduction Computer Intro. to Digital Analog Architecture Struct. VLSI IC Design IC Design Recommended Joachim Rodrigues, Assistant Professor Digital Intro. to Digital Henrik Sjöland, Professor IC Design Struct. VLSI IC Design Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Grading Scope A project course to give experience in practical design in • 9 ECTS a modern design environment. – 1 Assignment in UMC 130-nm CMOS Unique possibility to design an IC! – 4 presentations (5 min) – Report In groups of 2 students • 3 ECTS – First half of period 2 will be one assignment to learn the tools – Verification by Measurement – period 3 and 4 will be group projects – Report – verification part • FPGA: period 4 • ASIC: after the summer Total 12 credits, grade 3-5 (dependent on project and – applications mainly from signal processing performance) Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

“Labs” Assignment In period 2 you need to carry out one assignment which you will take through an entire digital ASIC design flow • 2 groups are set up for the labs, please sign up on course homepage. – Matrix multiplier (controller+datapath) • We will go through • RTL implementation • the ASIC synthesis flow • Simulation • ASIC Synthesis • Place and Route (PnR) – Area/speed constraint Schedule: • Physical placement and routing • TBD All tasks need to be completed in time to be able to continue • Thursday 13:15 – 15:15 with the project part of the course. The last two lab hours on due date TA’s will only approve the assignments. Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Matrix Multiplier ASIC Synthesis • Design Implementation • A new synthesis tool will be introduced • A matrix multiplier needs to be implemented in VHDL • Synopsys design compiler • 6x3 matrix, input vector • Time-multiplexed Architecture is (1 mult, 1add) • Designs needs to be constraint for: • Coefficients are stored in a ROM • Mimium area • Product needs to be stored in a RAM • Maximum speed • Memories will be provided • Netlist simulation • Design needs to be simulated with timing information generated during synthesis Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

Assignment Deadlines Physical Placement • A new tool will be introduced Deadlines MUST be met to be able to continue the course! • Cadence SoCEncounter • November 3 rd : FSMs and datapath • Memories and design needs to • November 10 th : Synthesizable model be placed and routed: • November 17 th : ASIC synthesis and netlist simulation • Floorplanning • November 24 rd : Physical placement and signal routing • Power Planning • Cell/Pad Placement • Clock tree synthesis • Signal routing Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Project Plagiasm Beginning of December projects will be conducted in groups of 2 students. New track: Computer Projects will be presented later Do not copy any material from other students or the Architecture internet. Examples from previous years – Pacemaker filter You will implement a RISC – UMTS filter processor on FPGA and you – FFT/DCT will run a program on it – Color converter – Gaussian filter EITF20 is a prerequisite for this – Divider using CORDIC track – Mixed radix FFT – Media Player Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

Project Grading 2009: 5 projects started Grade will depend on all parts of the course – 77 % passed – assignments – project results – oral presentations Dec March ca. 14 weeks – written report Usually the project/group is given the same grade. Final presentation However, individual grades might be given 1st presentation and report depending on the situation, e.g., group dynamics. Initial project presentation include • project specification • time ‐ plan • expected results Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Supervisors Students’ opinions • Positiv: – I got to know the whole process of the digital design follow. • Assignment – We can design our own chips,which is really exciting and – Nafiseh amazing. – Deepak – Man får se hela utvecklingskjedjan. – This is the most wonderful course I have studied. • Projects – En utmärkt kurs som verkligen förbereder ingenjörerna på – Johan verkliga problem i arbetslivet. En kurs som sammanfattar alla – Isael kunskaper och man får en känsla för hela processen från planering till färdig produkt. – Chenxin – Reza – Deepak – Yasser Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

Students’ opinions Life after • Negativ: Many students were able to get a Master Thesis at: • ST-Ericsson (6 students) – Information regarding the fact that verification (and • Ericsson (6 students) the course) extends over so many quarters. This • Infineon Austria (1 student) was not apparent when signing up for the course. • ARM (4 students) – we strongly suggest improving the credits to award the hard − working people a fair feedback. Outcome: – Lab manual should be more detail. • Publications 5: VTC (Taiwan), Globecom (Miami), Norchip (Scandinavia), Patmos (Delft) – The credits of this course is only 12 ECTS,I think • Patents 2 (Ericsson-STE) this number is too low. • PhD positions: 2 – We worked 7 months, full day, on it, actually. Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Questions? www.lu.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se Joachim Rodrigues, EIT, LTH jrs@eit.lth.se

Recommend

More recommend