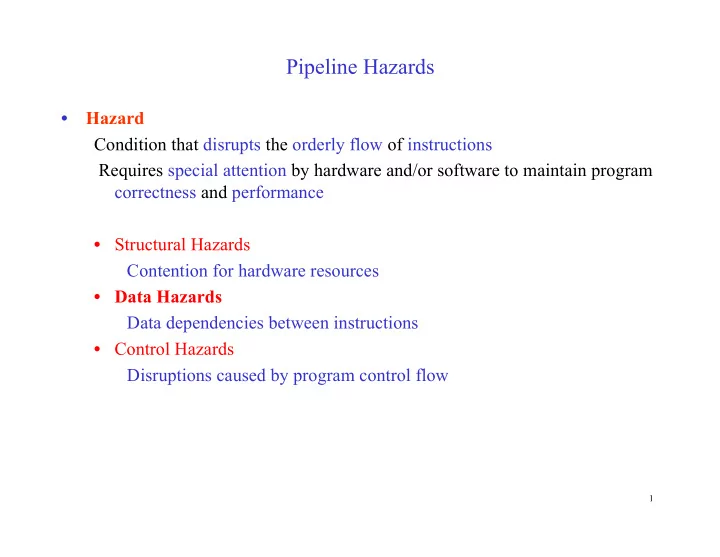

Pipeline Hazards Hazard Condition that disrupts the orderly flow - PowerPoint PPT Presentation

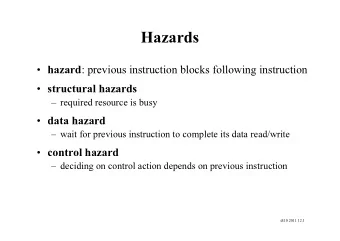

Pipeline Hazards Hazard Condition that disrupts the orderly flow of instructions Requires special attention by hardware and/or software to maintain program correctness and performance Structural Hazards Contention for hardware

Pipeline Hazards Hazard • Condition that disrupts the orderly flow of instructions Requires special attention by hardware and/or software to maintain program correctness and performance • Structural Hazards Contention for hardware resources • Data Hazards Data dependencies between instructions • Control Hazards Disruptions caused by program control flow 1

Data Dependencies Dependent instructions : access common storage location I 1 and I 2 instructions that access a common storage location • Read-after-Read ( RAR ) dependency • • I 2 reads the location read by I 1 I 1 : ADD R1, R2 , R3 I 2 : ADD R4, R5, R2 • Both I 1 and I 2 read register R2 Read-after-Write ( RAW ) dependency • • I 2 reads the location written by I 1 • No instruction between I 1 and I 2 writes to the same location I 1 : ADD R1 , R2, R3 I 2 : ADD R4, R1 , R2 • I 2 reads the value in register R1 that was written by I 1 2

Data Dependencies Dependent instructions : access common storage location I 1 and I 2 instructions that access a common storage location • Write-after-Read ( WAR ) dependency: • • I 2 writes the location read by I 1 I 1 : ADD R1, R2 , R3 I 2 : ADD R2 , R4, R5 • I 1 must read value of R2 prior to write by I 2 Write-after-Write ( WAW ) dependency: • • I 2 writes the location written by I 1 I 1 : ADD R1 , R2, R3 I 2 : ADD R1 , R4, R5 Write of R1 by I 1 must not occur after the write by I 2 • Final value of R1 due to write by I 2 and not I 1 • 3

When is a dependency a hazard? WAR Hazard A : ADD R1, R2 , R3 B : ADD R2 , R4, R5 1 2 3 4 5 6 A IF ID EX MEM WB IF ID EX MEM WB B 4

When is a dependency a hazard? WAR Hazard A : ADD R1, R2 , R3 B : ADD R2 , R4, R5 Register reads occur at an earlier pipeline stage than write • A reads R2 at cycle 2. • B writes R2 at cycle 6 (or later) • No WAR hazards in this pipelined implementation 1 2 3 4 5 6 A IF ID EX MEM WB IF ID EX MEM WB B 5

When is a dependency a hazard? WAW Hazard A : ADD R1 , R2, R3 B : ADD R1 , R4, R5 • Register writes occur only in WB stage • A writes R1 at cycle 5. • B writes R1 at cycle 6 (or later) • No WAW hazards in pipelined implementation 1 2 3 4 5 6 A IF ID EX MEM WB IF ID EX MEM WB B 6

When is a dependency a hazard? RAW Hazard A : ADD R1 , R2, R3 B : ADD R4, R1 , R5 • Hazard possible since register reads occur earlier than writes • A writes R1 at cycle 5 • B may read R1 at cycle 3, 4 or 5 Instruction B reads stale value in R1 before it is updated by A (HAZARD!!) Example: A and B consecutive instructions 1 2 3 4 5 6 A IF ID EX MEM WB IF ID EX MEM WB B 7

RAW Hazards 1 2 3 4 5 6 7 A IF ID EX MEM WB X IF ID EX MEM WB B IF ID EX MEM WB • A and B separated by 1 instruction: Hazard 1 2 3 4 5 6 7 8 A IF ID EX MEM WB X IF ID EX MEM WB Y IF ID EX MEM WB IF ID EX MEM WB B • A, B separated by 2 instructions • Hazard depends on register file design 8 • No Hazard with split read/write protocol with writes earlier in cycle

RAW Hazards 1 2 3 4 5 6 7 8 A IF ID EX MEM WB X IF ID EX MEM WB Y IF ID EX MEM WB IF ID EX MEM WB Z B IF ID EX MEM A, B separated by 3 instructions: No Hazard Register file design alternatives: 1. value returned by read equals the value being written at that cycle 2. value returned by read is the old value 1 implies no RAW hazard • 2 implies RAW hazard • 9

Pipeline Hazards Hazard • Condition that disrupts the orderly flow of instructions Requires special attention by hardware and/or software to maintain program correctness and performance • Structural Hazards Contention for hardware resources • Data Hazards Data dependencies between instructions • Control Hazards Disruptions caused by program control flow 10

Lazy Execution of Branch Equal Instruction : beq Rt, Rs, d IF ID EX MEM WB MUX AND PC PC P C C C + n n Decode + t PC 4 t r r l ADD l A (rs) REG F REG L L I FILE A n FILE G Mux U s (rt) IM t r u rs c rt t rd i o n << d d EXT 11

Control Hazards • Branch instruction disrupts the sequential instruction stream • For conditional branches need to determine Branch Outcome • For unconditional and taken conditional branches need to determine branch Target Address • Target Address : next instruction from a non-sequential address • Cannot fetch next instruction till target address computed • Do not know target address (at least) till branch instruction decoded • Branch Outcome: • Depends on internal state (e.g.register values) • Need to evaluate branch condition • May happen deep in the pipeline • Cannot know for certain which instructions to bring into pipeline • What if the incorrect instruction sequence is executed? Problem: Need to stall the pipeline till branch outcome is known and target address is computed. 12

Control Hazards A : beq R2, R3, L1 B • In our lazy design: the branch was resolved only in the MEM stage C D • The PC was updated with the target address only E at the end of cycle 4 --- • What happens to the pipeline? L1: P 13

Control Hazards 1 2 3 4 5 6 7 8 9 10 11 12 IF ID EX MEM WB A IF ID EX MEM WB B IF ID EX MEM WB C IF ID EX MEM WB D IF ID EX MEM WB P IF ID EX MEM WB Q IF ID EX MEM WB R • Instructions B, C, D will enter the pipeline while branch outcome is being determined • Need to make sure they do not compromise correctness • Want to reduce the performance degradation 14

Control (Branch) Hazards : Problems : The target address of the branch is not known (at least) till instruction is decoded • What is the address of instruction P? • The outcome of the branch (taken/ not taken) is determined deep in the pipeline • Should we execute B or P after A? • What should the pipeline (processor) do after fetching the branch instruction? We don’t know it’s a branch (at least for now) till instruction is in ID • Default execution will begin reading instruction B in IF • What then? • 15

Control Hazard A B IF ID EX MEM WB T = 1 B A C IF ID EX MEM WB T = 2 C B A D IF ID EX MEM WB T = 3 D C B A P IF ID EX MEM WB T = 4 16 TAKEN BRANCH

Simple Software Solution: Insert NOPs beqz R2, label Possible execution sequences: NOP Branch Not Taken: A , NOP, NOP, NOP, B NOP Branch Taken: A , NOP, NOP, NOP, P NOP B ----- • Adds 3 cycles to execution time for every branch label: P 1 2 3 4 5 6 7 8 9 IF ID EX MEM WB A NOP NOP NOP B IF ID EX MEM WB P 17

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.