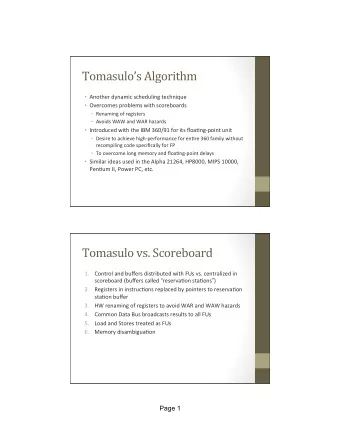

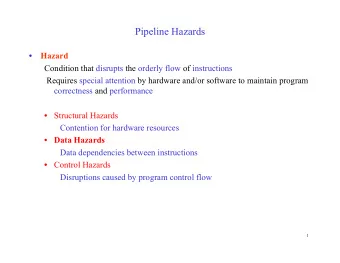

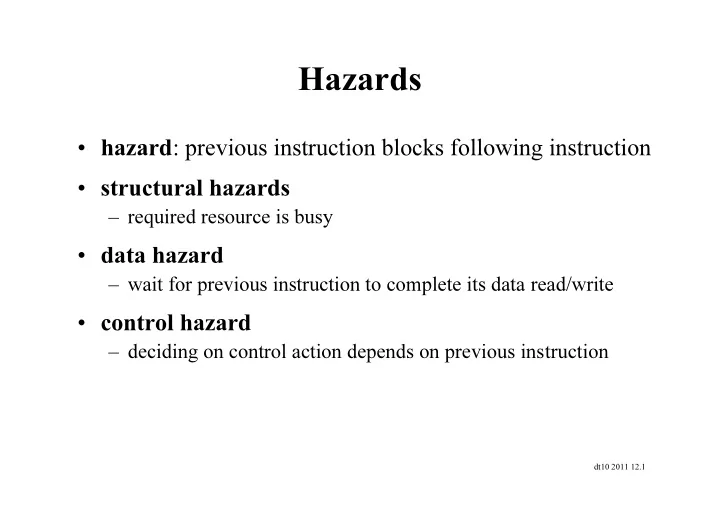

Hazards hazard : previous instruction blocks following instruction - PowerPoint PPT Presentation

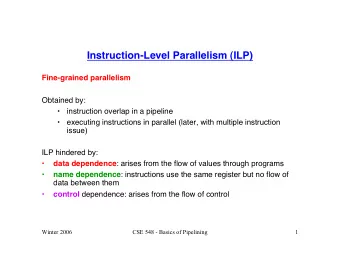

Hazards hazard : previous instruction blocks following instruction structural hazards required resource is busy data hazard wait for previous instruction to complete its data read/write control hazard deciding on

Hazards • hazard : previous instruction blocks following instruction • structural hazards – required resource is busy • data hazard – wait for previous instruction to complete its data read/write • control hazard – deciding on control action depends on previous instruction dt10 2011 12.1

Structural hazards • conflict for use of a resource • in MIPS pipeline with a single memory – load/store requires data access – instruction fetch: stall for that cycle causing a pipeline “bubble” • hence pipelined datapaths require – separate instruction/data memories – or separate instruction/data caches dt10 2011 12.2

Data hazards • an instruction depends on completion of data access by a previous instruction – add $s0, $t0, $t1 sub $t2, $s0, $t3 dt10 2011 12.3

Forwarding or bypassing • use result when it is computed – do not wait for it to be stored in a register – requires extra connections in the datapath dt10 2011 12.4

Load-use data hazard • cannot always avoid stalls by forwarding – if value not computed when needed – cannot forward backward in time! dt10 2011 12.5

Code scheduling to avoid stalls • reorder code to avoid use of load result in the next instruction • C code for A = B + E; C = B + F; lw $t1, 0($t0) lw $t1, 0($t0) lw $t2, 4($t0) lw $t2, 4($t0) add $t3, $t1, $t2 lw $t4, 8($t0) sw $t3, 12($t0) add $t3, $t1, $t2 lw $t4, 8($t0) sw $t3, 12($t0) add $t5, $t1, $t4 add $t5, $t1, $t4 sw $t5, 16($t0) sw $t5, 16($t0) 13 cycles 11 cycles dt10 2011 12.6

Control hazards • branch determines flow of control – fetching next instruction depends on branch outcome – pipeline can’t always fetch correct instruction – e.g. still working on ID stage of branch • In MIPS pipeline – compare registers and compute target early in the pipeline – have to add hardware to do it in ID stage dt10 2011 12.7

Stall on branch • wait until branch outcome determined before fetching next instruction dt10 2011 12.8

Branch prediction • longer pipelines cannot readily determine branch outcome early – stall penalty becomes unacceptable • predict outcome of branch – only stall if prediction is wrong • In MIPS pipeline – can predict branches not taken – fetch instruction after branch, with no delay dt10 2011 12.9

MIPS with prediction prediction correct prediction incorrect dt10 2011 12.10

More realistic branch prediction • static branch prediction – based on typical branch behavior – example: loop and if-statement branches predict backward branches taken predict forward branches not taken • dynamic branch prediction – hardware measures actual branch behavior e.g. record recent history of each branch – assume future behavior will continue the trend when wrong, stall while re-fetching, and update history – only maintain information about small number of branchs dt10 2011 12.11

Pipelined datapath dt10 2011 12.12

Pipelined control: simplified dt10 2011 12.13

Pipelined control • control signals derived from instruction – as in single-cycle implementation dt10 2011 12.14

dt10 2011 12.15

Data hazards in ALU instructions • consider instruction sequence: sub $2, $1, $3 and $12, $2, $5 or $13, $6, $2 add $14, $2, $2 sw $15, 100($2) • can resolve hazards with forwarding – how to detect when to forward? dt10 2011 12.16

Dependencies and forwarding dt10 2011 12.17

Detecting: need to forward • pass register numbers along pipeline – e.g. ID / EX.RegRS = register number for register RS sitting in ID/EX pipeline register • ALU operand register numbers in EX stage: given by – ID/EX.RegRS, ID/EX.RegRT • data hazards when Fwd from 1a. ID/EX.RegRS = EX/MEM.RegRD add $1,$2,$3 EX/MEM 1b. ID/EX.RegRT = EX/MEM.RegRD pipeline reg 2a. ID/EX.RegRS = MEM/WB.RegRD Fwd from RegRD RegRS RegRT MEM/WB 2b. ID/EX.RegRT = MEM/WB.RegRD pipeline reg dt10 2011 12.18

Detecting: need to forward IF/ID.RegRS ID/EX.RegRS EX/MEM.RegRD Fwd from • pass register numbers along pipeline EX/MEM pipeline reg – e.g. ID / EX.RegRS = register number for register RS sitting IF ID EX MEM WB in ID/EX pipeline register Fwd from MEM/WB pipeline reg • ALU operand register numbers in EX stage: given by IF/ID.RegRT ID/EX.RegRT MEM/WB.RegRD – ID/EX.RegRS, ID/EX.RegRT • data hazards when 1a. ID/EX.RegRS = EX/MEM.RegRD 1b. ID/EX.RegRT = EX/MEM.RegRD 2a. ID/EX.RegRS = MEM/WB.RegRD 2b. ID/EX.RegRT = MEM/WB.RegRD dt10 2011 12.19

�eed to forward: conditions • but only if forwarding instruction writes to a register! – EX/MEM.RegWrite, MEM/WB.RegWrite • and only if Rd for that instruction is not $0 – EX/MEM.RegRD ≠ 0, MEM/WB.RegRD ≠ 0 • When would we use $0 as a destination? dt10 2011 12.20

Forwarding paths dt10 2011 12.21

Forwarding conditions • EX hazard – if ( EX/MEM.RegWrite and (EX/MEM.RegRD ≠ 0) and (EX/MEM.RegRD = ID/EX.RegRS) ) then ForwardA = 10 – if ( EX/MEM.RegWrite and (EX/MEM.RegRD ≠ 0) and (EX/MEM.RegRD = ID/EX.RegRT) ) then ForwardB = 10 • MEM hazard – if ( MEM/WB.RegWrite and (MEM/WB.RegRD ≠ 0) and (MEM/WB.RegRD = ID/EX.RegRS) ) then ForwardA = 01 – if ( MEM/WB.RegWrite and (MEM/WB.RegRD ≠ 0) and (MEM/WB.RegRD = ID/EX.RegRT) ) then ForwardB = 01 dt10 2011 12.22

Double data hazard • consider the sequence: add $1,$1,$2 add $1,$1,$3 add $1,$1,$4 • both hazards occur – want to use the most recent • revise MEM hazard condition – only forward if EX hazard condition is not true dt10 2011 12.23

Revised forwarding condition • MEM hazard – if ( MEM/WB.RegWrite and (MEM/WB.RegRD ≠ 0) and (MEM/WB.RegRD = ID/EX.RegRS) and not ( EX/MEM.RegWrite and (EX/MEM.RegRD ≠ 0) and (EX/MEM.RegRD = ID/EX.RegRS) ) ) then ForwardA = 01 – if ( MEM/WB.RegWrite and (MEM/WB.RegRD ≠ 0) and (MEM/WB.RegRD = ID/EX.RegRT) and not (EX/MEM.RegWrite and (EX/MEM.RegRD ≠ 0) and (EX/MEM.RegRD = ID/EX.RegRT) ) ) then ForwardB = 01 dt10 2011 12.24

Datapath with forwarding dt10 2011 12.25

Load-use data hazard Need to stall for one cycle dt10 2011 12.26

Load-use hazard detection • check: when instruction is decoded in ID stage • ALU operand register numbers in ID stage are given by – IF/ID.RegRS, IF/ID.RegRT • load-use hazard when – ID/EX.MemRead and ( ( IF/ID.RegRS = ID/EX.RegRT ) or ( IF/ID.RegRT = ID/EX.RegRT ) ) • if detected, stall and insert bubble dt10 2011 12.27

How to stall the pipeline • force control values in ID/EX register to 0 – EX, MEM and WB do nop (no-operation) • prevent update of PC and IF/ID register – current instruction is decoded again – following instruction is fetched again – 1-cycle stall allows MEM to read data for lw • will forward to EX stage in next cycle dt10 2011 12.28

Stall/bubble in the pipeline Stall inserted here dt10 2011 12.29

Stall/bubble in the pipeline Or, more accurately� dt10 2011 12.30

Datapath with hazard detection dt10 2011 12.31

Summary: stalls and performance • stalls – reduce performance – but are required to get correct results • compiler – arranges code to avoid hazards and stalls – requires knowledge of the pipeline structure dt10 2011 12.32

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.