Paging Basic method Hardware support TLB Memory Protection - PowerPoint PPT Presentation

BS1 WS19/20 topic-based slides Paging Basic method Hardware support TLB Memory Protection Hierarchical Page Tables Hashed Page Tables Inverted Page Tables Shared Pages Virtual Address space under different

BS1 WS19/20 – topic-based slides Paging • Basic method • Hardware support • TLB • Memory Protection • Hierarchical Page Tables

• Hashed Page Tables • Inverted Page Tables • Shared Pages • Virtual Address space under different architectures • Paging Dynamics, Page faults • Working Sets • Page Replacement Strategies • Copy-On-Write Pages 2

Paging Dynamic storage allocation algorithms for varying-sized chunks of memory may ● lead to fragmentation Solutions: ● a) Compaction – dynamic relocation of processes b) Noncontiguous allocation of process memory in equally sized pages (this avoids the memory fjtting problem) Paging breaks physical memory into fjxed-sized blocks – page frames ● Logical memory is organized into pages of the same size ● paging is the process of dynamically mapping memory pages to page frames ● Operating Systems 15

Paging: Basic Method When a process is executed, its pages are loaded into any available ● frames from backing store (disk) Hardware support for paging consists of a page table ● Logical addresses consist of page number and ofgset ● CPU p d f d Logical Physical address address Physical memory p offset Page number Page frames are typically 16 2-4 kb Page table

Paging Example 0 1 Page 1 4 2 Page 0 0 1 1 3 Page 1 Page 3 6 2 4 Page 2 Page 0 3 3 Page 3 5 page Page 2 6 logical table memory 7 physical memory Operating Systems 17

Free Frames physical physical frame frame memory memory number number 7 7 Free frame list Page 1 8 8 7, 8, 10, 11,13, 16 9 9 Process creation 10 10 11 0 Page 0 11 11 8 1 12 12 16 2 Page 3 13 13 13 3 14 14 New process 15 15 page table Page 2 16 16 Free frame list 17 17 7, 10 After allocation Before allocation Operating Systems 18

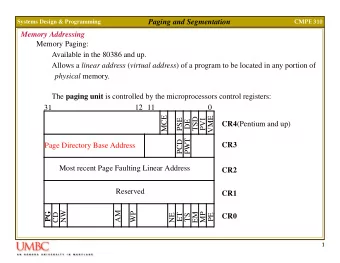

Paging: Hardware Support Every memory access requires access to the page table ● Page tables exist on a per-user process basis ● Page table should be implemented in hardware ● Small page tables can be just a set of registers ● Problem: size of physical memory, # of processes ● Page tables should be kept in memory ● Only base address of page table is kept in a special register (cr3 in x86) ● Problem: memory accesses is slow ● Solution: Translation look-aside bufgers (TLBs) ● Associative registers store recently used page table entries ● TLBs are fast, expensive, small: 8..2048 entries ● TLB must be fmushed on process context switches ● Operating Systems 19

Associative Memory ● Associative memory – parallel search Page # Frame # Address translation (A´, A´´) ● If A´ is in associative register, get frame # out. ● Otherwise get frame # from page table in memory Operating Systems 20

Paging Hardware With TLB CPU p d f d Logical Physical TLB hit address address offset Page # Frame # Page number TLB Physical memory p TLB miss Page table Operating Systems 21

Efgective Access Time with TLB Associative Lookup in TLB = ε time unit; ● Assume memory cycle time is 1μs; with ε << 1μs ● Hit ratio – percentage of times that a page number is found in the ● associative registers; ratio related to number of associative registers and process workload. ● Let us assume a hit ratio = α ● Efgective Access Time (EAT) ● EAT = (1μs + ε ) α + (2μs + ε ) (1 – α ) Operating Systems 22

Memory Protection ● Memory protection implemented by associating control bits with each page frame reference in the page table ● Isolation of processes in main memory ● Valid-invalid bit attached to each entry in the page table: ● “valid” indicates that the associated page is in the process’ logical address space, and is thus a legal page ● “invalid” indicates that the page is not in the process’ logical address space ● access to invalid page produces a page fault Operating Systems 23

Valid (v) or Invalid (i) Bit in a Page Table ● Invalid pages may simply be paged out frame number 0 Page 1 1 4 v 0 Page 0 1 v 1 2 Page 1 6 v 2 Page 3 3 Page 2 3 v 3 Page 0 4 Page 3 i 4 5 i 5 logical Page 2 6 page memory table 7 physical memory Operating Systems 24

Hierarchical Page Tables ● Break up the logical address space into multiple page tables ● “fmat” Page tables are too large ● nested levels of page tables can be allocated as necessary ● allows for large pages ● A simple technique is a two-level page table ● Used with 32-bit CPUs Operating Systems 25

Two-Level Paging Example A logical address (on 32-bit machine with 4K page size) is divided into: ● a page number consisting of 20 bits. ● a page ofgset consisting of 12 bits. ● Since the page table is paged, the page number is further divided into: ● a 10-bit page number page number ● page offset a 10-bit page ofgset ● p 2 p i d Thus, a logical address is as follows: ● 10 12 10 where p i is an index into the outer page table, and p 2 is the displacement within the page of the outer page table Operating Systems 26

Two-Level Page-Table Scheme … … … outer page table (page directory) … page tables memory Operating Systems 27

Address-Translation Scheme page number page offset p 2 p 1 d 10 10 12 p 1 Main memory ● Address-translation p 2 page scheme for a two- directory level 32-bit paging page architecture table Operating Systems 28

Hashed Page Tables ● Common in address spaces > 32 bits ● IA64 supports hashed page tables ● The virtual page number is hashed into a page table. This page table contains a chain of elements hashing to the same location ● Virtual page numbers are compared in this chain searching for a match. If a match is found, the corresponding physical frame is extracted Operating Systems 29

Hashed Page Table CPU p d f d Logical Physical address address Physical memory offset Page number hash p f q r function Page table Operating Systems 30

Inverted Page Table ● One entry for each real page of memory ● Entry consists of the virtual address of the page stored in that real memory location, with information about the process that owns that page ● Decreases memory needed to store each page table, but increases time needed to search the table when a page reference occurs ● Use hash table to limit the search to one — or at most a few — page-table entries Operating Systems 31

Inverted Page Table Architecture CPU pid p d f d Logical Physical address address Physical memory offset Page number Process ID f pid p search Page table Operating Systems 32

Shared Pages ● Shared code ● One copy of read-only (reentrant) code shared among processes (i.e., text editors, compilers, window systems) ● Shared code must appear in same location in the logical address space of all processes ● Private code and data ● Each process keeps a separate copy of the code and data ● The pages for the private code and data can appear anywhere in the logical address space Operating Systems 33

Shared Pages Example frame number Process 1 Process 1 page table 0 virtual memory cpp 1 1 cpp 2 4 cc1 3 11 cc2 cc1 4 7 data1 5 6 Process 2 Process 2 page table virtual memory data1 7 1 data2 cpp 8 4 cc1 9 11 cc2 10 8 cc2 data2 11 memory Operating Systems 34

Segmentation with Paging The innovative MULTICS operating system introduced: Logical addresses: 18-bit segment no, 16-bit ofgset ● (relatively) small number of 64k segments ● To eliminate fragmentation, segments are paged ● A separate page table exists for each segment ● physical d memory s d yes logical address >= p d‘ no segment page-table + Trap length base + f f d‘ segment table segment table physical address base register 35 page table for segment s

Intel 30386 Address Translation Intel logical selector offset Address The Intel 386 uses descriptor s table segmentation limit base with paging for + memory Physical Address 31 22 21 12 11 0 Intel Linear 10 10 12 management with Address a two-level paging operand scheme. 4 Kb page PTE 4Kb PDE 4KiB frame 22 bit Page table operand offset 1024 entries 4Mb PDE 4 Mb page 4MiB frame Page directory Physical Memory cr 3 1024x4byte entries Operating Systems 36 (one per process) Physical address

Address Translation Mapping via page table entries ● Indirect relationship between virtual pages and physical memory ● user Virtual pages x86: Physical memory 31 22 21 12 11 0 system 10 10 12 Page directory user index Page table index Byte index Page table system entries Operating Systems 2

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.