Outline PACIFIC: SiPM Readout Introduction 1 PACIFIC 2 - PowerPoint PPT Presentation

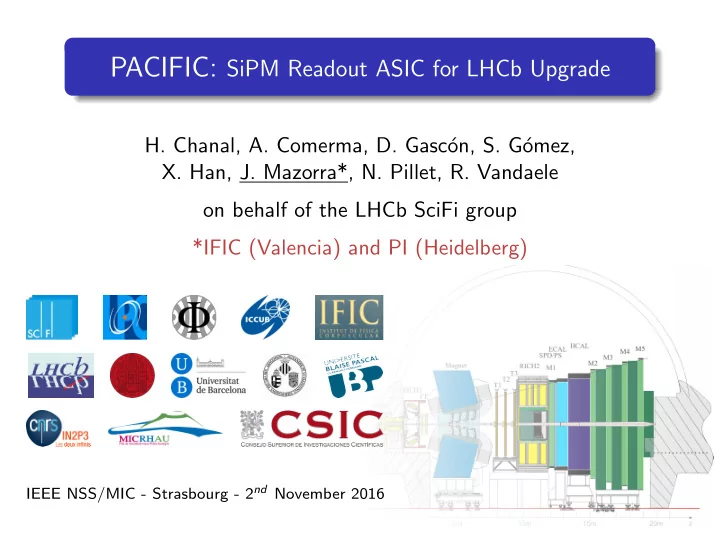

PACIFIC: SiPM Readout ASIC for LHCb Upgrade H. Chanal, A. Comerma, D. Gasc on, S. G omez, X. Han, J. Mazorra*, N. Pillet, R. Vandaele on behalf of the LHCb SciFi group *IFIC (Valencia) and PI (Heidelberg) IEEE NSS/MIC - Strasbourg - 2 nd

PACIFIC: SiPM Readout ASIC for LHCb Upgrade H. Chanal, A. Comerma, D. Gasc´ on, S. G´ omez, X. Han, J. Mazorra*, N. Pillet, R. Vandaele on behalf of the LHCb SciFi group *IFIC (Valencia) and PI (Heidelberg) IEEE NSS/MIC - Strasbourg - 2 nd November 2016

Outline PACIFIC: SiPM Readout Introduction 1 PACIFIC 2 Preamplifier Shaper Integrator Digitizer Prototypes 3 PACIFICr0/1 PACIFICr2/3 Outlook 4

Introduction: LHCb PACIFIC: SiPM Readout Physics measurements limited by 1 MHz hardware trigger. Introduction Upgrade: increased luminosity, PACIFIC 40 MHz trigger at front-end. Preamplifier Shaper Integrator New detector for T1-T3 Digitizer the Scintillating Fibre Tracker. Prototypes PACIFICr0/1 PACIFICr2/3 3 stations x 4 planes (x-u-v-x). Outlook 12 modules per plane. 6 layer fibre mats (mirrored). 8x2 . 5 m mats per module. 2 ROB (top/bottom) with 16 SiPMs and FE electronics. 1 / 15

PACIFIC PACIFIC: Readout with 64 channel in CMOS 130 nm ( IBM → TSMC ). SiPM Readout Current mode input for direct anode connection. Introduction Configurable non-linear digital output serialized. PACIFIC Fast shaping to minimize spillover. Preamplifier Shaper Integrator Signal integration to overcome low photostatistics Digitizer using dual interleaved system to avoid dead time. Prototypes PACIFICr0/1 Single photoelectron detection capability. PACIFICr2/3 Outlook 2 / 15

PACIFIC: Preamplifier PACIFIC: Double feedback current conveyor: Bandwidth 250 MHz. SiPM Readout Fix input voltage and impedance. Input impedance 50 Ω . Selectable gains at output mirror. Introduction Input voltage control Transimpedance amplifier: range 700 mV. PACIFIC Preamplifier Current to voltage conversion. Input dynamic Shaper Integrator Control conveyor output voltage. range 4 µ A-4 mA. Digitizer Power consumption Prototypes below 2 mW. PACIFICr0/1 PACIFICr2/3 Outlook 3 / 15

PACIFIC: Shaper PACIFIC: Double pole-zero cancellation scheme for fast shaping (10 ns). SiPM Readout Closed-loop OTA circuit with two configurable passive nets: First pole-zero net cancels slow component Introduction (SiPM capacitance and quenching resistor). Second pole-zero net cancels fast component PACIFIC Preamplifier (trace parasitics and input impedance). Shaper Integrator A DC feedback loop controls the quiescent output voltage Digitizer (critical for the subsequent integration). Prototypes PACIFICr0/1 PACIFICr2/3 Outlook Double PZ Shaper 4 / 15

PACIFIC: Integrator PACIFIC: Classic closed-loop gated integrator architecture SiPM Readout based on a Miller OTA with increased slew rate. Dead times avoided by using two interleaved units Introduction with independent offset trimming circuits. PACIFIC Synchronization with the digitizer is mandatory. Preamplifier Shaper Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook Dual Gated Integrator 5 / 15

PACIFIC: Digitizer PACIFIC: SiPM Readout Dual passive track and hold merges the two subchannels. Introduction Flash ADC using three comparator with: PACIFIC Preamplifier Dynamic range: 20-850 mV. Shaper Integrator Hysteresis: 10 mV. Digitizer Prototypes Three independent references, PACIFICr0/1 configurable per channel, with: PACIFICr2/3 Dynamic range: 0-750 mV. Outlook Resolution: 8 bits. Hysteresis Comparator The output of two channels is fed to a serializer that: encodes the three comparator outputs into 2 bits. streams out both values at 160 MHz. 6 / 15

PACIFICr0 and PACIFICr1 PACIFIC: SiPM Readout PACIFICr0: May 2013. Introduction IBM 130 nm. PACIFIC Fix gain current conveyor. Preamplifier Design migration from Shaper Integrator AMS 350 nm BiCMOS. Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 PACIFICr1: Outlook November 2013. IBM 130 nm. One analog FE plus test blocks. Analog external bias. Independent GI output. 7 / 15

PACIFICr1: Linearity PACIFIC: Good Preamplifier linearity over full designed dynamic range. SiPM Readout Introduction PACIFIC Preamplifier Shaper Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook 8 / 15

PACIFICr2 and PACIFICr3 PACIFIC: SiPM Readout PACIFICr2: Introduction August 2014. PACIFIC IBM 130 nm. Preamplifier Eight full FE channels. Shaper Integrator Internal biasing and Digitizer I2C digital configuration. Prototypes PACIFICr0/1 PACIFICr2/3 Outlook PACIFICr3: July 2015. TSMC 130 nm. First full size prototype. Separate bias left/right. 9 / 15

PACIFICr3: Power and Bias PACIFIC: SiPM Readout Power consumption 10 . 4 mW/ch , within specifications. Bandgap and derived reference voltages slightly low. Introduction All reference voltage use the same DAC design (6 bit) PACIFIC except the threshold of the first comparator (7 bit). Preamplifier Shaper Reasonably linear response in all measured instances. Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook 10 / 15

PACIFICr3: Input Voltage PACIFIC: Derived from a resistor ladder with 16 possible values. SiPM Readout Range (700 mV) and step (50 mV) as simulated. Introduction PACIFIC Preamplifier Shaper Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook 11 / 15

PACIFICr3: Integration Window PACIFIC: Internal charge injection triggered externally. SiPM Readout Output sorted by trigger to clock phase difference. Response limited by integrator slew rate. Introduction PACIFIC Preamplifier Shaper Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook 12 / 15

PACIFICr3: Comparator Mismatch PACIFIC: SiPM Readout Comparator offset voltage obtained using threshold scan. Calculated difference to the first comparator offset voltage. Introduction All channels in two chips evaluated, 256 instances in total. PACIFIC Preamplifier Shaper Measured 20 % increase w.r.t. Monte Carlo simulations. Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook 13 / 15

PACIFICr3: Synchronous Light Input PACIFIC: Picosecond diode laser synchronously pulsed on SiPM. SiPM Readout Distinct photoelectron structures are noticeable. Processing channel architecture considered validated. Introduction PACIFIC Preamplifier Shaper Integrator Digitizer Prototypes PACIFICr0/1 PACIFICr2/3 Outlook 14 / 15

Outlook PACIFIC: SiPM Readout PACIFIC is a SiPM readout ASIC with: Current input for direct anode connection. Introduction Fast PZ cancellation shaping for tail suppression. Gated integrator damps statistical fluctuations. PACIFIC Preamplifier Non-linear configurable 2 bit digital output. Shaper Integrator Digitizer Channel architecture has been fully validated. Prototypes PACIFICr0/1 PACIFICr2/3 New prototype PACIFICr4 is in production with: Outlook Increased slew rate in integrator amplifier. Expanded comparator transistor size a factor three, in addition threshold DACs per channel included. Custom digital output pads with higher driving power. Production readiness review planned for Q2 2017. 15 / 15

Thanks a lot for your attention!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.