Outline Paper presentation Ultra-Portable Devices Log-Likelihood - PowerPoint PPT Presentation

Outline Paper presentation Ultra-Portable Devices Log-Likelihood Algebra Paper: Principles for the analog decoding design Factor graphs J. Hagenauer, E. Offer, C. Measson, M. Mrz. Building blocks for analog decoder

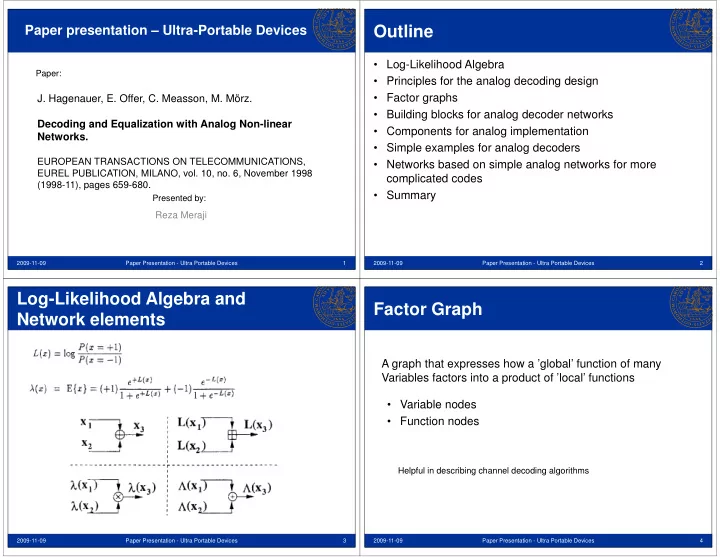

Outline Paper presentation – Ultra-Portable Devices • Log-Likelihood Algebra Paper: • Principles for the analog decoding design • Factor graphs J. Hagenauer, E. Offer, C. Measson, M. Mörz. • Building blocks for analog decoder networks Decoding and Equalization with Analog Non-linear • Components for analog implementation Networks. Networks. • Simple examples for analog decoders EUROPEAN TRANSACTIONS ON TELECOMMUNICATIONS, • Networks based on simple analog networks for more EUREL PUBLICATION, MILANO, vol. 10, no. 6, November 1998 complicated codes (1998-11), pages 659-680. • Summary Presented by: Reza Meraji 2009-11-09 Paper Presentation - Ultra Portable Devices 1 2009-11-09 Paper Presentation - Ultra Portable Devices 2 Log-Likelihood Algebra and Factor Graph Network elements A graph that expresses how a ’global’ function of many Variables factors into a product of ’local’ functions • Variable nodes • Function nodes • Function nodes Helpful in describing channel decoding algorithms 2009-11-09 Paper Presentation - Ultra Portable Devices 3 2009-11-09 Paper Presentation - Ultra Portable Devices 4

Hamming Code Memory one convolutional code • Rate ½ • Code length 16 • Tailbiting structure 2009-11-09 Paper Presentation - Ultra Portable Devices 5 2009-11-09 Paper Presentation - Ultra Portable Devices 6 Memory two convolutional code Trellis representation • Rate ½ • Tanner graphs: • [7,5] encoder graphs with hidden or auxiliary variables and • N information bits variables which are not necessarily binary • States as hidden variables 2009-11-09 Paper Presentation - Ultra Portable Devices 7 2009-11-09 Paper Presentation - Ultra Portable Devices 8

Tailbiting convolutional codes Code Block Length • Achieve the minimum distance of block codes for short and medium block sizes • Long block lengths are a great challenge for the analog technique • No need for termination bits • Less complexity for analog decoder • Analog decoding on short block length might be used as an inner decoder system to perform a first and quick clean up of errors • Certain constraint for block length – Ex. For memory two and rate = ½: Need for a circle size of at least 11 information bits 2009-11-09 Paper Presentation - Ultra Portable Devices 9 2009-11-09 Paper Presentation - Ultra Portable Devices 10 Building blocks for analog Building blocks for analog decoder networks decoder networks, continue • BJT • Another function needed in node variables: Algebraic sum of L-values • Summing voltages: opamp with external resisotrs -> not • Gilbert Cell: a well known multiplier suitable for analog VLSI • An alternative: Using the Gilbert cells -> great advantage for • An alternative: Using the Gilbert cells -> great advantage for • Boxplus operation: layout Differential output current of Gilbert Cell made of BJT • Boxplus and variable sum circuits: each 9 transistors transistors 2009-11-09 Paper Presentation - Ultra Portable Devices 11 2009-11-09 Paper Presentation - Ultra Portable Devices 12

Simple examples for analog Bulding Blocks: example decoders • Block length 3 • Memory 1 • Check equation: • Rate = ½ • Tailbiting convolutional code code • Circle size: 8 information bits • u = (-1, -1, -1, +1, -1, +1, -1, -1) 2009-11-09 Paper Presentation - Ultra Portable Devices 13 2009-11-09 Paper Presentation - Ultra Portable Devices 14 Simple examples for analog Simple examples for analog decoders decoders • A decoder network with two or three • Memory 2 edges leaving one variable node needs • Rate = ½ additional information • Tailbiting convolutional code • Case for Hamming code and memory • Case for Hamming code and memory • Circle size: 16 information • Circle size: 16 information two convolutional code bits • Eq. 35 2009-11-09 Paper Presentation - Ultra Portable Devices 15 2009-11-09 Paper Presentation - Ultra Portable Devices 16

Analog decoder for Hamming Hamming Turbo code Code 2009-11-09 Paper Presentation - Ultra Portable Devices 17 2009-11-09 Paper Presentation - Ultra Portable Devices 18 Codes with higher number of Hamming Turbo Simulations connections • ML decoding performance is only achieved when variable nodes are sparsely connected • In general, no great achievement out of simulations • However, most efficient coding schemes are characterized by sparsely connected variable nodes 2009-11-09 Paper Presentation - Ultra Portable Devices 19 2009-11-09 Paper Presentation - Ultra Portable Devices 20

Analog decoder networks based Analog decoder networks based on Trellises on Trellises • Extension of box-plus operations • As long as a trellis of the code preserves a ”butterfly” structure • In this case message passing is equivalent to forward- backward algorithm (BCJR) 2009-11-09 Paper Presentation - Ultra Portable Devices 21 2009-11-09 Paper Presentation - Ultra Portable Devices 22 Summary • Analog, non-linear and highly parallel decoder networks instead of digital processors • Box-plus element as the key element corresponding to binary addition in GF(2) • Non-linearities of bipolar transistors utalized to build the key elements elements • From factor graphs to simple analog VLSI implementations • Soft values are needed as inputs • Decoder network may not converge • Mapping of binary trellis onto box-plus circuits 2009-11-09 Paper Presentation - Ultra Portable Devices 23 2009-11-09 Paper Presentation - Ultra Portable Devices 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.