Memory Errors Bits in memory can be flipped Hard error The chip is - PowerPoint PPT Presentation

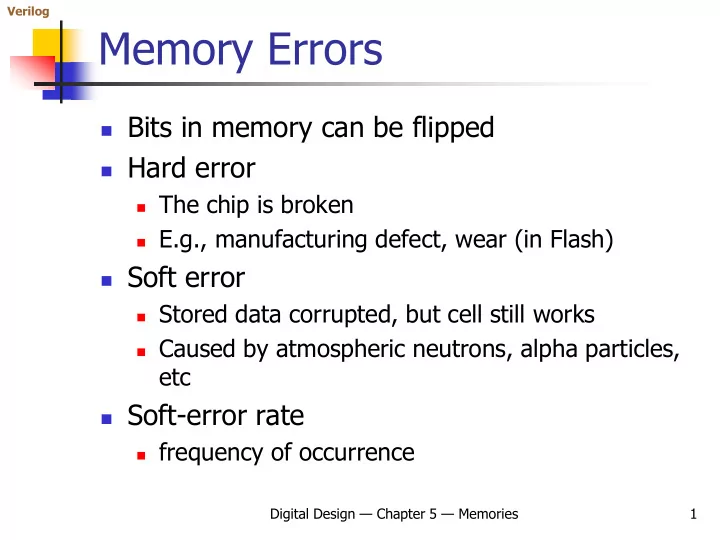

Verilog Memory Errors Bits in memory can be flipped Hard error The chip is broken E.g., manufacturing defect, wear (in Flash) Soft error Stored data corrupted, but cell still works Caused by atmospheric neutrons, alpha

Verilog Memory Errors Bits in memory can be flipped Hard error The chip is broken E.g., manufacturing defect, wear (in Flash) Soft error Stored data corrupted, but cell still works Caused by atmospheric neutrons, alpha particles, etc Soft-error rate frequency of occurrence Digital Design — Chapter 5 — Memories 1

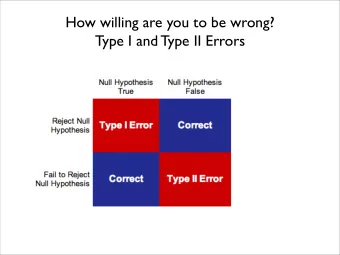

Verilog Error Detection using Parity Add a parity bit to each location On write access compute data parity and store with data On read access check parity, take exception on error If we could tell which bit flipped correct by flipping it back, then write back to memory location Can’t do this with parity Digital Design — Chapter 5 — Memories 2

Verilog Error-Correcting Codes (ECC) Allow identification of the flipped bit Hamming Codes E.g., for single-bit-error correction of N -bit word, need log 2 N + 1 extra bits Example: 8-bit word, d 1 ... d 8 12-bit ECC code, e 1 ... e 12 e 1 , e 2 , e 4 , e 8 are check bits, the rest data d 8 d 7 d 6 d 5 d 4 d 3 d 2 d 1 e 12 e 11 e 10 e 9 e 8 e 7 e 6 e 5 e 4 e 3 e 2 e 1 Digital Design — Chapter 5 — Memories 3

Verilog Hamming Code Example e 1 = e 3 ⊕ e 5 ⊕ e 7 ⊕ e 9 ⊕ e 11 d 8 d 7 d 6 d 5 d 4 d 3 d 2 d 1 e 2 = e 3 ⊕ e 6 ⊕ e 7 ⊕ e 10 ⊕ e 11 e 12 e 11 e 10 e 9 e 8 e 7 e 6 e 5 e 4 e 3 e 2 e 1 0 0 0 1 e 1 e 4 = e 5 ⊕ e 6 ⊕ e 7 ⊕ e 12 0 0 1 0 e 2 0 1 0 0 e 4 e 8 = e 9 ⊕ e 10 ⊕ e 11 ⊕ e 12 1 0 0 0 e 8 0 0 1 1 e 3 Every data bit covered by two 0 1 0 1 e 5 or more check bits 0 1 1 0 e 6 On write: Compute check bits 0 1 1 1 e 7 1 0 0 1 and store with data e 9 1 0 1 0 e 10 1 0 1 1 e 11 1 1 0 0 e 12 Digital Design — Chapter 5 — Memories 4

Verilog Hamming Code Example On read: Recompute check bits and XOR with read check bits result called the syndrome 0000 => no error 0 0 0 1 e 1 0 0 1 0 e 2 If data bit flipped 0 1 0 0 e 4 covering bits of syndrome are 1 1 0 0 0 e 8 = binary code of flipped ECC bit 0 0 1 1 e 3 If stored check bit flipped 0 1 0 1 e 5 0 1 1 0 e 6 that bit of syndrome is 1 0 1 1 1 e 7 On error, unflip bit and rewrite 1 0 0 1 e 9 memory location 1 0 1 0 e 10 1 0 1 1 e 11 1 1 0 0 e 12 Digital Design — Chapter 5 — Memories 5

Verilog Multiple-Error Detection What if two bits flip syndrome identifies wrong bit, or is invalid One extra check bit allows single-error correction, double-error detection Single-bit correction Double-bit detection N Check bits Overhead Check bits Overhead 8 4 50% 5 63% 16 5 31% 6 38% 32 6 19% 7 22% 64 7 11% 8 13% 128 8 6.3% 9 7.0% 256 9 3.5% 10 3.9% Digital Design — Chapter 5 — Memories 6

Verilog Summary Memory: addressable storage locations Read and Write operations Asynchronous RAM Synchronous RAM (SSRAM) Dynamic RAM (DRAM) Read-Only Memory (ROM) and Flash Multiport RAM and FIFOs Error Detection and Correction Hamming Codes Digital Design — Chapter 5 — Memories 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.