LDO application and design requirements Carlo.Fiocchi - AMS Italy - PowerPoint PPT Presentation

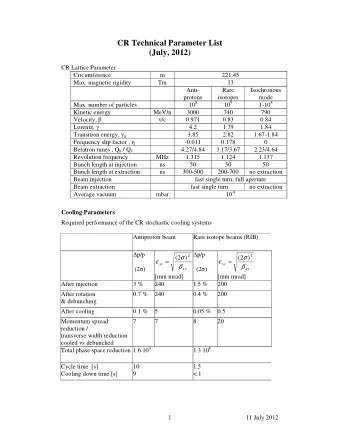

LDO application and design requirements Carlo.Fiocchi - AMS Italy CAS Workshop 2017 Almo Collegio Borromeo - Pavia 21 March 2017 Page 1 Introduction LDO design is quite, I would say extremely, specific. May be none of the attendee will

LDO application and design requirements Carlo.Fiocchi - AMS Italy CAS Workshop 2017 Almo Collegio Borromeo - Pavia 21 March 2017 Page 1

Introduction LDO design is quite, I would say extremely, specific. May be none of the attendee will consider this topic in the future. Nevertheless it is possible to make fruitful a discuss on it, even in the very short duration of this lesson It is not a matter to show in details any design aspect and how the solutions are effectively implemented The matter is so wide, so many proposed solutions are found in literature, that this cannot be solved in 1 hour and half. Moreover such a lesson, for those not fully concerned, would result boring soon. On the contrary, we can take a great advantage from LDO critical design challenges: this kind circuit has an intrinsic weakness in stability, usually the hot topic of any conference, lesson and paper. The poor safety margin affecting stability is the cause of frequent particular problems. They look quite surprising indeed, like - AC bode diagram with 90deg PM and incapable to predict the instability shown by a transient simulation - extremely large noise of an amplifier, much larger than the expected result. - an AC supply disturbance might cause an error in a High resolution ADC converter for DC signals Only an interpretation which is at the same time original and strict would allow a clear view to solve these problems and go ahead. Reporting these interpretations, and the associated achievements, is interesting by itself: they cannot be found in paper, lessons but they are useful to open anyone’s mind At the same time they can be exploited in other design activities, even totally different from LDO applications: even if usually the safety margins for stability are superior and prevent the encountered problems to be triggered, the same might pop up if trying to outperforming what is at the state of the art. If not understood and solved, solutions advantageous from a theorical point of view should be abandoned to choose simpler but surely less performing ones Hence, these kind of learnt lessons from LDO design challenge has an inestimable value. So let’s take the opportunity offered by today conference Page 2

Basic LDO specs A voltage source satisfying the following requirements: - Low drop regulation small voltage between voltage supply and regulated voltage - Accuracy Vin Vreg - Large current sourcing capability its output acts as a supply for a load LDO - Capability to sustain large capacitors at the load - PSRR - Provide a clean, ripple-free and noise-reduced, regulated voltage Page 3 3

LDO Architecture The above mentioned requirements bring to a well defined architecture Vin Vref output transistor is a PMOS device: Vds copes low drop needs better than NMOS Vgs A allow large swing at PMOS gate: ensures large drive capability even in triode conditions R2 R1 amplification stage after a virtual ground: Minimizes output voltage variations after load changes continuous time system: no ripple is a key feature, unlike switching converters. No clock. Page 4 4

LDO Architecture Vin Specification for each building block Vref A Amplifier stage: rail to rail output swing moderately high gain A R2 Cload R1 PMOS device: Large size if in triode, must be capable to sustain the maximum load current with few tenths mV drop Load capacitor interaction with internal nodes for stability concerns: dominant pole determination Page 5 5

Why an LDO? A) it splits power management sources to avoid interaction of noisy parts B) Concerns about HV supply voltage: area and CMOS circuitry implementation C) Filtering supply noise Page 6 6

Why an LDO? Vin power management source splitting to avoid interaction of noisy parts Vref G1 Mpout R2 Vreg1 In case Iload2 has large and frequent transient Iload R1 variations, Vreg1 is not disturbed by them Vin Frequently adopted in mixed signal applications Vreg1 and Vreg2 might also be different, to have a Mpout G1 degree of freedom for analog section dynamic range and better dissipation for the digital side R3 Vreg2 Iload2 R4 Page 7 7

Why an LDO? Concerns about HV supply voltage: area and PMOS CMOS circuitry implementation HV vs. LV - A CMOS gate cannot usually sustain more than few Volts voltage (say from 1.8V to 5V), largely less than a battery supply (around 42V). Scaling down supply is mandatory NMOS - A CMOS circuit for HV robustness need area consuming protections and the minimum width does not go below some µ m: HV vs. LV Page 8 8

Why an LDO? Filtering supply noise Vin an LDO is just a bit more sophisticated opamp. Vref Hence its PSRR, if optimized, can be used to A suppress supply noise Any variation at the supply is corrected by the feedback loop at the gate of the output transistor R2 Cload and only a small error affects the error amplifier R1 input thanks to the amplifier stage A. As a result the regulated output is affected by a remarkably attenuated version of the error on the supply line Page 9 9

Why an LDO instead of possible alternatives? DC-DC switching regulator vs. LDO DCDC switching controller converter Vref I Vin Vref A LDO regulator R2 Cload R1 Page 10

DC-DC switching regulator vs. LDO LDO implementation An output transistor (either N or P-type) inside a feedback loop drives the output current. An error amplifier and a voltage divider complete the feedback regulation by comparing the target output to the real one and drive the gate of the output transistor. Vref power Erramp transistor R2 R1 Page 11

DC-DC switching regulator vs. LDO DCDC implementation A controller senses the load voltage and eventually current: duty cycle of the clocked signal that drives the output digital driver is consequently set. A cascaded LC circuit filters out the average value and provides the regulated voltage Vout to the load controller Vref I Page 12

DC-DC switching regulator vs. LDO Vin Efficiency performance - The LDO dissipates in the output stage : Vout P_diss = Iload*(Vin-Vout) Iload - The switching regulator dissipation depends on the Vdd output transistors on-resistance Ron. Hence: 2 P_diss = Ron * Iload Vout Vsw => A DCDC regulator has key advantage vs. LDO once Ron*Iload << (Vin-Vout) I - LDO requires much less bias current: => A winning feature for light loads Vdd Vout Vsw GND Page 13

DC-DC switching regulator vs. LDO DC-DC switching regulator outperforms LDO: - switching regulator for step up has no LDO counterpart - better efficiency at high load current - better efficiency at high (Vin - Vout) drops LDO outperforms DC-DC switching regulator - less external components - better efficiency at low currents and low Vin-Vout - less noisy: no ripple affects the regulated voltage - smaller pin count (commercial devices having 3 pins only) Page 14

LDO applications Where to use an LDO? Take into account two contraddictory features: 1) Poor efficiency vs switching converters: large values for (VIN-VOUT) and load current are detrimental. 2) LDO analog performances largely outperform DCDC switching regulators’. => A very popular solution is to combine LDOs with DCDC converters Page 15

LDO applications LDO cascaded to DCDC converter: both positive features combined: Vin Vsys DCDC Trade off on efficiency: coil switching the largest portion of (Vin – Vout) Vref Vout is sustained by the DCD switching LDO driver regulator. LDO operates with limited voltage R2 room, set by the intermediate supply Vsys. R1 Remarkable: to suppress switching noise, avoid LDO GBW near DCDC clock where PSRR is usually at the worst value and peaking might occur Page 16

LDO key parameters Dropout It refers to the minimum supply voltage that ensures Vreg accurate enough definition: dropout as (Vin - Vout ) value when Vout drops 100mV (or a TBD % of Vout_nominal) under a decrease in Vin Page 17

LDO key parameters - Dropout Vin - key parameter for prolonged battery life Vref - specified at different load currents A - specified at different Vout variants: be careful R2 equivalent circuit: Cload R1 - large input error brings PMOS gate at GND, open loop condition - Vdropout = Vds = ron *Iload Mpout - ron = k/(Vgs-Vth) = k/(Vin-Vth) Vreg Larger output transistor improves dropout value (but not recommended to save area) Iload Other drawbacks are associated to bigger device (more parasitics) => Dropout sets the output transistor size. Page 18

ACCURACY It is the combination of many contributes - precision in the reference voltage Vref, usually a trimmed bandgap - Offset of the LDO input stage and feedback resistor matching not a major concern as soon as Vref trimming takes this error too into account. - Variation in the supply voltage (line regulation) - Variation in the load current Among the above listed contributes, only the ones that depend on operating conditions are troublesome, while the others are corrected by trimming. Temperature drift is a minor error once a bandgap is used (worst case 80-100ppm/C° i.e. 1% in 100/125 degrees variation) Page 19 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.