Introduction Paper presentation Ultra-Portable Devices Paper: - PowerPoint PPT Presentation

Introduction Paper presentation Ultra-Portable Devices Paper: Viterbi algorithm by analog components (Add-compare- select) C. Winstead, C. Schlegel. Analog Decoding: the State of the Art Fully parallel analog soft iterative

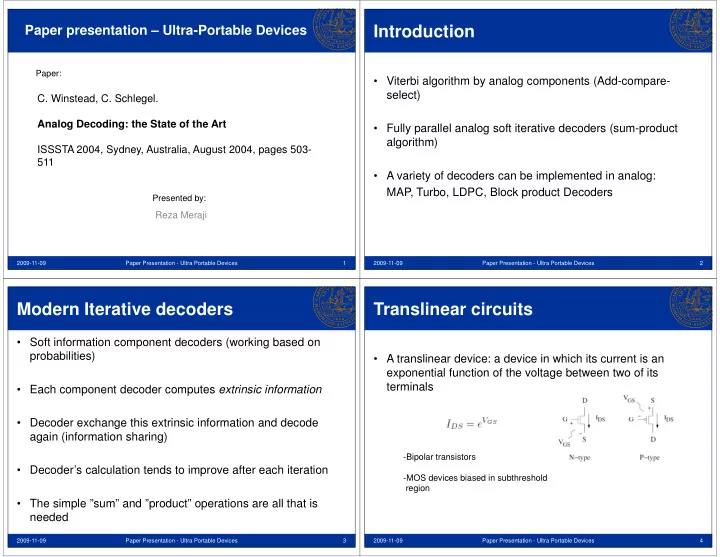

Introduction Paper presentation – Ultra-Portable Devices Paper: • Viterbi algorithm by analog components (Add-compare- select) C. Winstead, C. Schlegel. Analog Decoding: the State of the Art • Fully parallel analog soft iterative decoders (sum-product algorithm) algorithm) ISSSTA 2004, Sydney, Australia, August 2004, pages 503- 511 • A variety of decoders can be implemented in analog: MAP, Turbo, LDPC, Block product Decoders Presented by: Reza Meraji 2009-11-09 Paper Presentation - Ultra Portable Devices 1 2009-11-09 Paper Presentation - Ultra Portable Devices 2 Modern Iterative decoders Translinear circuits • Soft information component decoders (working based on probabilities) • A translinear device: a device in which its current is an exponential function of the voltage between two of its terminals • Each component decoder computes extrinsic information • Decoder exchange this extrinsic information and decode again (information sharing) -Bipolar transistors • Decoder’s calculation tends to improve after each iteration -MOS devices biased in subthreshold region • The simple ”sum” and ”product” operations are all that is needed 2009-11-09 Paper Presentation - Ultra Portable Devices 3 2009-11-09 Paper Presentation - Ultra Portable Devices 4

Translinear circuits Basic Computational Elements • Analog currents proportional to probabilities • Translinear circuits for analog multiplications • Shorting wires for summation Translinear circuits can be used for Sum and product operations are provided by translinear devices multiplication of currents Log-domain processing? => work with voltages 2009-11-09 Paper Presentation - Ultra Portable Devices 5 2009-11-09 Paper Presentation - Ultra Portable Devices 6 CMOS Analog Decoders CMOS Analog decoders • MOS transistors in weak inversion or subthreshold region • Suitable for SOC design: – Rejection of high frequency interferences • Current is typically less than 100 nA – Produces no high-frequency interference • The transistor is never ”turned on” -> leakage in digital design • Performance: • Performance: – Block length up to 256 coded bits • Consumed power in the transistor in the nano Watt range – Throughput up to 500 Mbit/s (1 Mbit/s for low voltage/power) • The transistor is slow => high throughput is obtained through • Extremely low energy operation parallelism 2009-11-09 Paper Presentation - Ultra Portable Devices 7 2009-11-09 Paper Presentation - Ultra Portable Devices 8

Interfacing with a larger system Analog Decoder Interface • Serial to parallel conversion (S/H circuits) • Channel information expressed as a sequence of differential voltages (LLRs) • Parasitic effects – Clock feed-through (or charge injections) – Substrate leakage • Analog-Digital interface 2009-11-09 Paper Presentation - Ultra Portable Devices 9 2009-11-09 Paper Presentation - Ultra Portable Devices 10 Some Challenging Issues Some Challenging Issues Simulations • Mismatch and larger decoders (8,4) Hamming decoder, Importance sampling results for a Performance loss due to mismatch for regular LDPC simulated using importance sampling (16,11)^2 analog product decoder codes, based on Density Evolution 2009-11-09 Paper Presentation - Ultra Portable Devices 11 2009-11-09 Paper Presentation - Ultra Portable Devices 12

Summary • Iterative algorithms for analog decoders • Translinear circuits as decoder building blocks • CMOS analog decoders • Interface architecture • Performance evaluation 2009-11-09 Paper Presentation - Ultra Portable Devices 13

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.