Gem5 in a nutshell Christophe Huriaux, Post-doc Inria, IRISA CAIRN - PowerPoint PPT Presentation

Gem5 in a nutshell Christophe Huriaux, Post-doc Inria, IRISA CAIRN Project-Team CAIRN project-team SAV 2016 June 30th-July 1st 2016 - 1 1 Spoiler alert Not a research report ... but a (quick) overview of how Gem5 works and

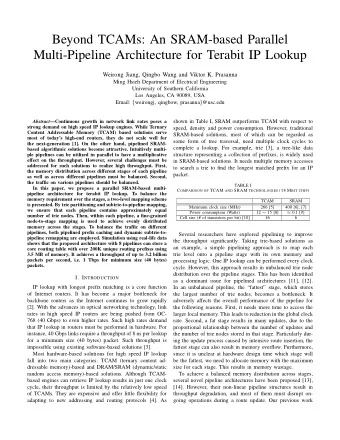

Gem5 in a nutshell Christophe Huriaux, Post-doc Inria, IRISA — CAIRN Project-Team CAIRN project-team — SAV 2016 June 30th-July 1st 2016 - 1 1

Spoiler alert § Not a research report… § ... but a (quick) overview of how Gem5 works and what it can offer CAIRN project-team — SAV 2016 - 2 June 30th-July 1st 2016 2

Outline § Introduction § What is Gem5 useful for ? (or rather: what you should not use it for) § Overview of the system simulator § Simulation modes § Behind the scene of a simulation § What’s under the hood ? § Memory system § Running example § Conclusion CAIRN project-team — SAV 2016 - 3 June 30th-July 1st 2016 3

Introduction § Gem5 is the fusion of two projects § GEMS : simulation of multi-processor systems § M5 : simulation of networked systems § System simulator § Accurate simulation of complex components interactions (OS / CPU / Caches / Devices / …) § Accuracy depends on the model completeness § All-in-one simulation framework § Don’t rely on other software § But we can plug them in easily… § Lot of components available out-of-the-box § (CPUs, memories, I/Os, …) CAIRN project-team — SAV 2016 - 4 June 30th-July 1st 2016 4

What is Gem5 useful for ? Architectural exploration ? Yes ! 👎 Gem5 provides a fast and easy framework to interconnect hardware components and evaluate them ! Hardware/software performance evaluation ? Yes ! 👎 Gem5 have a good support of various ISA and allows for realistic HW/SW performance evaluation. CAIRN project-team — SAV 2016 - 5 June 30th-July 1st 2016 5

What is Gem5 useful for ? Hardware/software verification ? No … 👏 RTL functional verification is much more mature and accurate ! Software development and verification ? Ugh.. Please stop! 👏 👏 👏 Faster technologies are available through binary-translation (e.g. QEMU, OVP) CAIRN project-team — SAV 2016 - 6 June 30th-July 1st 2016 6

Simulation modes § Full-system (FS) § Models bare-metal hardware § Includes the various specified devices, caches, … § Boots an entire OS from scratch § Gem5 can boot Linux (several variants) or Android out- of-the-box § Syscall Emulation (SE) § Runs a single static application § System calls are emulated or forwarded to the host OS § Lot of simplifications (address translation, scheduling, no pthread …) CAIRN project-team — SAV 2016 - 7 June 30th-July 1st 2016 7

Behind the scene of a simulation Compilation of the simulator C++ C++ / Python Collection of Simulator components internals Gem5 binary CAIRN project-team — SAV 2016 - 8 June 30th-July 1st 2016 8

Behind the scene of a simulation Simulation ! Python script instanciating the component hierarchy and defining simulation parameters Python interpreter Collection of component Assembled C++ interfaces objects Simulation Gem5 binary Output (statistics, traces…) CAIRN project-team — SAV 2016 - 9 June 30th-July 1st 2016 9

What’s under the hood ? Simulation objects 1 component = 1 simulation object + .py .cc C++ / Python Python interface C++ functional Collection of model (for instanciation) components (for simulation) § SimObjects follow a strict C++ class hierarchy for easier extension with code reuse … BaseCPU ClockedObject BaseTimingCPU SimObject BaseO3CPU … … CAIRN project-team — SAV 2016 - 10 June 30th-July 1st 2016 10

What’s under the hood ? Events § Gem5 is event-driven § Discrete event timing model § Not related to real time whatsoever § The real time duration of 1 tick can be user- defined § Simulation objects schedule events for the next cycle of after a specific time elapsed § The Gem5 simulation scheduler takes care of the rest ! CAIRN project-team — SAV 2016 - 11 June 30th-July 1st 2016 11

What’s under the hood ? Memory ports § Memory ports are present on every MemObject § They model physical memory connections § You interconnect them during the hierarchy instanciation § E.g. a CPU data bus to a L1 cache § Work by pairs: 1 master port always connect to 1 slave port Inst. S M S M S M DDR3 L1$ X CPU bar Data M S M S M S Flash L1$ § Data is exchanged atomically as packets CAIRN project-team — SAV 2016 - 12 June 30th-July 1st 2016 12

What’s under the hood ? Memory ports § 3 types of transport interfaces for packets § Functional § Instantaneous in a single function call § Caches and memories are updated automagically at once § Atomic § Instantaneous § Memory model updated (caches, coherence …) § Approximate latency, but no contention nor delay § Timing § Transaction split into multiple phases § Models all timing in the memory system § The transport interface depends on the SimObject implementation CAIRN project-team — SAV 2016 - 13 June 30th-July 1st 2016 13

Memory system One memory system to rule them all… § Models a system running heterogeneous applications… § … running on heterogeneous processing tiles § ... using heterogeneous memories and interconnect CPU CPU CPU CPU CPU CPU CPU GPU Accelerators Interconnect … DDR3 SRAM Flash CAIRN project-team — SAV 2016 - 14 June 30th-July 1st 2016 14

Memory system …and in the simulation, interconnect them § Two memory systems in Gem5 § Classic § All components instanciated in a hierarchy along with CPUs, etc. § MOESI coherence protocol only § Ruby § Detailed simulation model of various cache hierarchies § Various cache coherence protocols (MESI, MOESI, …) § Interconnection networks § Classic is faster but less detailed CAIRN project-team — SAV 2016 - 15 June 30th-July 1st 2016 15

Running example Is my FFT faster with more processors ? Hardware/software performance evaluation ! 👎 Let’s evaluate ! § FFT kernel from the SPLASH2 benchmark suite § ARM Instruction Set Architecture § 1 or 4 out-of-order detailed CPUs § Caches § L1: 64kb data, 32kb instruction § L2: 2Mb, shared CAIRN project-team — SAV 2016 - 16 June 30th-July 1st 2016 16

Conclusion § Quick introduction to Gem5 § Much more things to explore in the framework ! § Integration of power models in development § Memory / CPU traces generation § Statistics output for performance evaluation § SystemC co-simulation § Automatic benchmark run § Checkpointing, fast-forwarding CAIRN project-team — SAV 2016 - 17 June 30th-July 1st 2016 17

Thank you for your attention J CAIRN project-team — SAV 2016 June 30th-July 1st 2016 - 18 18

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.