Floorplanning and Topology Generation for Application-Specific - PowerPoint PPT Presentation

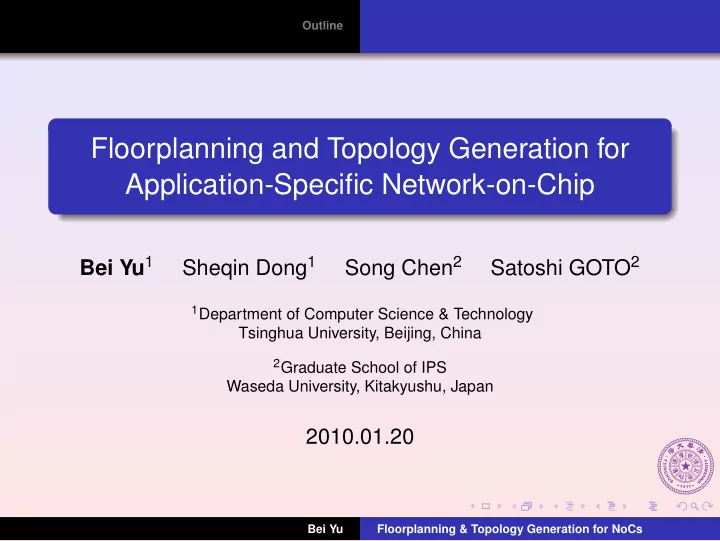

Outline Floorplanning and Topology Generation for Application-Specific Network-on-Chip Bei Yu 1 Sheqin Dong 1 Song Chen 2 Satoshi GOTO 2 1 Department of Computer Science & Technology Tsinghua University, Beijing, China 2 Graduate School of

Outline Floorplanning and Topology Generation for Application-Specific Network-on-Chip Bei Yu 1 Sheqin Dong 1 Song Chen 2 Satoshi GOTO 2 1 Department of Computer Science & Technology Tsinghua University, Beijing, China 2 Graduate School of IPS Waseda University, Kitakyushu, Japan 2010.01.20 Bei Yu Floorplanning & Topology Generation for NoCs

Outline Outline Introduction 1 Previous Works Problem Formulation Topology Synthesis Algorithm 2 Partition Driven Floorplanning Switches and Network Interfaces Insertion Energy Aware Path Allocation Experimental Results 3 Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Previous Works Algorithm Problem Formulation Experimental Results Network-on-Chip Solution to global communication challenges Alternative to Bus communication architectures Better modularity Lower power consumption Scalability Regular NoCs and Application-Specific NoCs Network components: Switch Network Interface (NI) S=Switch S S S NI NI NI NI VU SRAM Node Node Node NI SDRAM NI NI S S S S NI NI NI Media samp S CPU NI Node Node Node calc NI NI NI S S S S NI NI NI NI RISC SRAM DSP CPU Node Node Node Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Previous Works Algorithm Problem Formulation Experimental Results Regular or Application-Specific Topology Regular Topology Task Scheduling and Mapping problem Application-Specific Topology? Irregular core sizes 1 Different communication flow requirements 2 Reducing energy by reducing hop count and switch count 3 Possibly higher performance 4 S=Switch S S S NI NI NI NI VU SRAM Node Node Node NI SDRAM NI NI S S S S NI NI NI Media samp S CPU NI Node Node Node calc NI NI NI S S S S NI NI NI NI RISC SRAM DSP CPU Node Node Node Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Previous Works Algorithm Problem Formulation Experimental Results Regular or Application-Specific Topology Regular Topology Task Scheduling and Mapping problem Application-Specific Topology? Irregular core sizes 1 Different communication flow requirements 2 Reducing energy by reducing hop count and switch count 3 Possibly higher performance 4 Focus on Application-Specific Topology Generation! S=Switch S S S NI NI NI NI VU SRAM Node Node Node NI SDRAM NI NI S S S S NI NI NI Media samp S CPU NI Node Node Node calc NI NI NI S S S S NI NI NI NI RISC SRAM DSP CPU Node Node Node Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Previous Works Algorithm Problem Formulation Experimental Results Previous Works – K.Srinivasan et al. TVLSI 06 : Used fixed floorplan as optimization starting point Switch at corners of cores – Murali et al. ICCAD06 : Two steps topology generation procedure using min-cut partitioner Greedy based path allocation assignment – Chan & Parameswaran, ASPDAC08 : Iterative refinement strategy supports both packet-switched networks and point to point connections – Murali et al. ASPDAC09 : Synthesis approach for 3D NoC LP based switch position computation Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Previous Works Algorithm Problem Formulation Experimental Results Motivations In previous works : Partition w/o physical information Fail to consider area consumption of NI and Switch In our works : Integrate partition into floorplanning phase Consider Switches and NI area consumption Min-Cost-Flow algorithm to insert NI Effective paths allocation to minimize power consumption Bei Yu Floorplanning & Topology Generation for NoCs

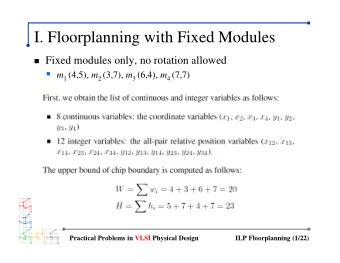

Introduction Previous Works Algorithm Problem Formulation Experimental Results Problem Formulation v1 v3 Input : v2 v4 a set of n cores C = { c 1 , c 2 , . . . , c n } . switches number m . core communication graph(CCG). v5 v6 network components power model. Output : an NoC topology satisfying CCG: Core Communication Graph. minimize area consumption. minimize the communication energy. Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Previous Works Algorithm Problem Formulation Experimental Results Synthesis Algorithm v1 v3 Obtain min-cut partitions of CCG v2 v4 Communication Requirement s1 s2 Distances between cores Cores in a cluster share a switch v5 Switch Communication Graph(SCG) v6 s3 Path Allocation on SCG Minimize power consumption s2 Minimize hop-count Satisfy width constraints s1 s3 SCG Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Overview of Algorithm Floorplanning Core Size Generate new floorplan CCG Partition Generate floorplan with partitions. No Yes c3 Stop? Post-Floorplanning c4 Switches Insertion c2 c1 Network Interfaces Insertion Path Allocation Optimized Floorplan Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Overview of Algorithm Floorplanning Core Size Generate new floorplan CCG Partition Insert Switches. No Yes c3 Stop? s2 s1 Post-Floorplanning c4 Switches Insertion c2 c1 Network Interfaces Insertion Path Allocation Optimized Floorplan Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Overview of Algorithm Floorplanning Core Size Generate new floorplan CCG Partition Insert NI with Min-Cost Flow Algorithm. No Yes c3 NI Stop? s2 NI NI NI s1 Post-Floorplanning c4 Switches Insertion c2 c1 Network Interfaces Insertion Path Allocation Optimized Floorplan Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Overview of Algorithm Floorplanning Core Size Generate new floorplan CCG Dynamic Programming based Partition Path Allocation. No Yes c3 NI Stop? s2 NI NI NI s1 Post-Floorplanning c4 Switches Insertion c2 c1 Network Interfaces Insertion Path Allocation Optimized Floorplan Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Partition Driven Floorplanning Traditionally, partition before floorplanning (-)Lose physical information In our work Integrate partition into floorplanning Cores with larger communication incline to one cluster Minimize interconnect power consumption Define new edge weight w ′ ij in CCG: max w + α d × mean dis w ij w ′ ij = α w × dis ij Using CBL 1 as topological representation Record white space information 1 X. Hong et al, IEEE Transaction on CAS 2004. Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Switches Insertion After floorplanning stage c3 Each cluster has a minimal bounding box. Heuristical method to insert switches: c4 Switch initially in the center of 1 c2 c1 bounding box. Partition the white space into grids. 2 Sort switches. 3 Insert switches in grids one by one. 4 In cluster p k , cost of insert switch k to grid g : � w ij × ( dis gi + dis gj ) , ∀ e ij ∈ ¯ Cost gk = E i , j Choose free grid with smallest Cost . Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Switches Insertion After floorplanning stage c3 Each cluster has a minimal bounding box. Heuristical method to insert switches: c4 s2 s1 Switch initially in the center of 1 c2 c1 bounding box. Partition the white space into grids. 2 Sort switches. 3 Insert switches in grids one by one. 4 In cluster p k , cost of insert switch k to grid g : � w ij × ( dis gi + dis gj ) , ∀ e ij ∈ ¯ Cost gk = E i , j Choose free grid with smallest Cost . Bei Yu Floorplanning & Topology Generation for NoCs

Introduction Partition Driven Floorplanning Algorithm Switches and Network Interfaces Insertion Experimental Results Energy Aware Path Allocation Switches Insertion After floorplanning stage 7 10 c3 Each cluster has a minimal bounding box. 6 9 5 8 Heuristical method to insert switches: 1 2 3 4 c4 s2 s1 Switch initially in the center of 1 c2 c1 bounding box. Partition the white space into grids. 2 Sort switches. 3 Insert switches in grids one by one. 4 In cluster p k , cost of insert switch k to grid g : � w ij × ( dis gi + dis gj ) , ∀ e ij ∈ ¯ Cost gk = E i , j Choose free grid with smallest Cost . Bei Yu Floorplanning & Topology Generation for NoCs

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![a b 1 b [ i ] 0 i 1 5 / 1 5 / a [ j ] j 0 j 0 = = a [ j ] b [ i j ] 0](https://c.sambuz.com/842727/a-b-1-b-i-0-i-1-5-1-5-a-j-j-0-j-0-a-j-b-i-j-0-0-s.webp)