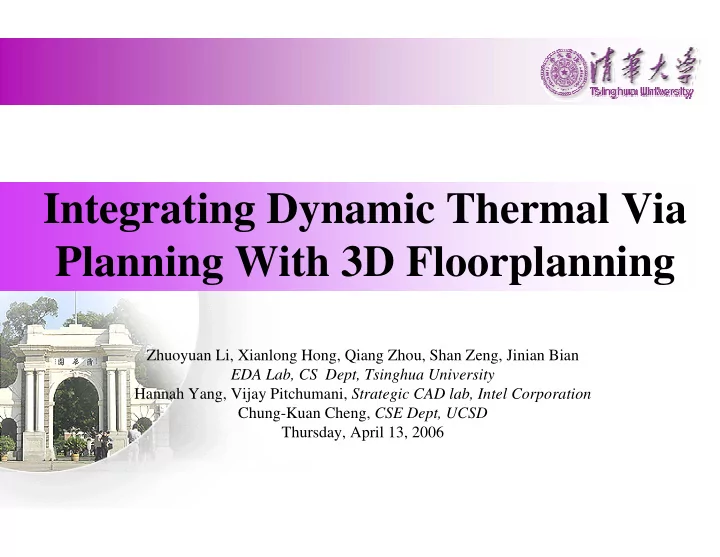

Integrating Dynamic Thermal Via Planning With 3D Floorplanning - PowerPoint PPT Presentation

Integrating Dynamic Thermal Via Planning With 3D Floorplanning Zhuoyuan Li, Xianlong Hong, Qiang Zhou, Shan Zeng, Jinian Bian EDA Lab, CS Dept, Tsinghua University Hannah Yang, Vijay Pitchumani, Strategic CAD lab, Intel Corporation Chung-Kuan

Integrating Dynamic Thermal Via Planning With 3D Floorplanning Zhuoyuan Li, Xianlong Hong, Qiang Zhou, Shan Zeng, Jinian Bian EDA Lab, CS Dept, Tsinghua University Hannah Yang, Vijay Pitchumani, Strategic CAD lab, Intel Corporation Chung-Kuan Cheng, CSE Dept, UCSD Thursday, April 13, 2006

Outline � Background � Background � Previous Work � Previous Work � Thermal Via Planning � Thermal Via Planning - Thermal Model - Thermal Model - Heuristic Method & Divide Heuristic Method & Divide- -and and- -conquer Method conquer Method - - Our Contribution Our Contribution - � Our Solution � Our Solution - Analytical solution for detailed thermal via distribution Analytical solution for detailed thermal via distribution - - Integrating thermal via planning into 3D floorplanning Integrating thermal via planning into 3D floorplanning - � Experimental Results � Experimental Results � Conclusion � Conclusion 4/13/2006 ISPD 2006, San Jose CA 2

Background � 3D Integration: Driving Forces � 3D Integration: Driving Forces - Improved global Improved global Interconnect Interconnect performance performance - - Reduce Reduce footprint footprint / Improve packing density / Improve packing density - - “ “Mixed Signal Mixed Signal” ” Integration Integration - � Challenges for 3D Integration � Challenges for 3D Integration - Heat Dissipation Heat Dissipation - - Reliability Reliability - - Design Complexity Design Complexity - 4/13/2006 ISPD 2006, San Jose CA 3

Previous Work � UCLA, Prof. Jason � UCLA, Prof. Jason Cong Cong’ ’s s Group Group - Thermal Thermal- -driven driven 3D floorplanning, ICCAD 3D floorplanning, ICCAD’ ’04 04 - - 3D global routing with 3D global routing with thermal via planning thermal via planning, ASP , ASP- -DAC DAC’ ’05 05 - - Post Post- -floorplanning floorplanning thermal via planning thermal via planning, ICCAD , ICCAD’ ’05 05 - - MEVA MEVA- -3D: Performance evaluation in 2D/3D designs, ASP 3D: Performance evaluation in 2D/3D designs, ASP- -DAC DAC’ ’06 06 - � UMN, Prof. Sachin � UMN, Prof. Sachin Sapatnekar Sapatnekar’ ’s s Group Group - Thermal-driven 3D placement, ICCAD’03 - - Post Post- -placement placement thermal via planning thermal via planning, ISPD , ISPD’ ’05 05 - Thermal Thermal- -driven driven 3D global routing, ASP 3D global routing, ASP- -DAC DAC’ ’06 06 - � Gatech � Gatech, , thermal thermal/power noise/congestion optimization in 3D ICs /power noise/congestion optimization in 3D ICs (ISCAS’ ’04, ASP 04, ASP- -DAC DAC’ ’04 & ASP 04 & ASP- -DAC DAC’ ’05) 05) (ISCAS � MIT, 3D placement & routing tool for � MIT, 3D placement & routing tool for wirelength wirelength/performance and /performance and thermal optimization optimization thermal (ASP- -DAC DAC’ ’03 & ISPD 03 & ISPD’ ’04) 04) (ASP � U Wisconsin, Chip � U Wisconsin, Chip- -level 3D level 3D Thermal Analysis Thermal Analysis Tool Tool (ISPD (ISPD’ ’03) 03) 4/13/2006 ISPD 2006, San Jose CA 4

Thermal Model � Resistive Thermal Model � Resistive Thermal Model (CFD Research Corporation) - The 3D circuit stack is divided by a two The 3D circuit stack is divided by a two- -dimensional array of tile dimensional array of tile - stacks. Each tile stack is composed of several vertically- stacks. Each tile stack is composed of several vertically -stacked tiles, stacked tiles, one from each device layer. one from each device layer. - These tile stacks are connected by lateral thermal resistances. These tile stacks are connected by lateral thermal resistances. Within Within - each tile stack, a thermal resistor is modeled for each device layer. ayer. each tile stack, a thermal resistor is modeled for each device l - Through solving the linear system - Through solving the linear system RT = P RT = P , the temperature on each , the temperature on each node could be determined. node could be determined. 4/13/2006 ISPD 2006, San Jose CA 5

Thermal Via Planning � Thermal Vias � Thermal Vias - Lowering the thermal resistance between Lowering the thermal resistance between - different layers different layers 1 1 1 = + - Thermal resistance: Thermal resistance: - R R R e layer via � T � T- -Via number should be minimized and they are Via number should be minimized and they are placed to hot areas to make the greatest impact. placed to hot areas to make the greatest impact. � Heuristic Method for T � Heuristic Method for T- -Via Planning Via Planning I 4 =Q Q Layer 4 - Thermal via number is in proportional to the Thermal via number is in proportional to the - Inter-layer I 3 =2Q Q Layer 3 heat flow inside that tile heat flow inside that tile Inter-layer Layer 2 = I 2 =3Q Q : : n n I I j k j k Inter-layer Layer 1 I 1 =4Q Q - Thermal via number in the figure is Thermal via number in the figure is - Substrate = : : 1 : 2 : 3 n n n 4 3 2 4/13/2006 ISPD 2006, San Jose CA 6

Thermal Via Planning � Heuristic Method (ASP � Heuristic Method (ASP- -DAC DAC’ ’05 & ISPD 05 & ISPD’ ’05) 05) 1. Initialize tile grids on floorplanning/placement results; 1. Initialize tile grids on floorplanning/placement results; 2. Temperature analysis by solving linear equations; 2. Temperature analysis by solving linear equations; 3. If temperature constraint is satisfied, exit; 3. If temperature constraint is satisfied, exit; 4. Update heat flow in each tile; 4. Update heat flow in each tile; 5. Assign thermal vias to each tile; 5. Assign thermal vias to each tile; 6. Update thermal resistance of each tile, Goto 2. 6. Update thermal resistance of each tile, Goto 2. � Divide � Divide- -and and- -conquer Method (ICCAD conquer Method (ICCAD’ ’05) 05) - Given initial floorplanning results, determine vertical and hor Given initial floorplanning results, determine vertical and horizontal izontal - thermal via distribution sequentially; thermal via distribution sequentially; - Vertical thermal via distribution: analytical solution; Vertical thermal via distribution: analytical solution; - - Horizontal thermal via distribution with - Horizontal thermal via distribution with heuristic method heuristic method. . - Implemented in a multi Implemented in a multi- -level global routing framework. level global routing framework. - � Drawbacks: (i) The heuristic method cannot generate optimal T � Drawbacks: (i) The heuristic method cannot generate optimal T- -Via Via planning; (ii) It is too time consuming to be integrated into floorplanning planning; (ii) It is too time consuming to be integrated into floorplanning 4/13/2006 ISPD 2006, San Jose CA 7

Our Contributions � Analytical solution for thermal via planning � Analytical solution for thermal via planning = - Heuristic method: Heuristic method: - : : n n I I i j i j = : : : Vertical n n I I i j i j - Divide Divide- -and and- -conquer method: conquer method: - = : : : Horizontal n n I I i j i j = : : n n I I - Our solution Our solution - i j i j 1. Optimal solution for detailed thermal via distribution; 1. Optimal solution for detailed thermal via distribution; 2. Analytical solution with low computational complexity. 2. Analytical solution with low computational complexity. � Integrate thermal via planning into hierarchical 3D � Integrate thermal via planning into hierarchical 3D floorplanning floorplanning - Inter Inter- -layer partition problem to minimize total number of thermal layer partition problem to minimize total number of thermal - vias are formulated and solved. are formulated and solved. vias - Fast white space redistribution to generate Fast white space redistribution to generate floorplans floorplans feasible for feasible for - thermal via insertion. thermal via insertion. 4/13/2006 ISPD 2006, San Jose CA 8

Our Solution: V-TV Distribution � Thermal conductivity calculation � Thermal conductivity calculation = + ( − 1 ) K m K m K i via i layer � The relationship between � The relationship between R R and and K K = α l × R K s � Temperature rise on the � Temperature rise on the i -th layer th layer i - k i k ∑ ∑ ∑ = + + ( ) T R P R P T i b j l j amb = = = 1 2 j l j l = = ( ) ( ) T F R F m i i 4/13/2006 ISPD 2006, San Jose CA 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![COMMUNICATING [with empathy] @ DY DYNAMIC JILL JILL @ DY DYNAMIC JILL TENSION IS INEVITABLE @](https://c.sambuz.com/548934/communicating-s.webp)