Floorplanning ECE6133 Physical Design Automation of VLSI Systems - PowerPoint PPT Presentation

Floorplanning ECE6133 Physical Design Automation of VLSI Systems Prof. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology Floorplanning, Placement, and Pin Assignment Partitioning leads to Blocks

Floorplanning ECE6133 Physical Design Automation of VLSI Systems Prof. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Floorplanning, Placement, and Pin Assignment • Partitioning leads to – Blocks with well-defined areas and shapes (fixed blocks). – Blocks with approximated areas and no particular shapes (flexible blocks). – A netlist specifying connections between the blocks. • Objectives – Find locations for all blocks. – Consider shapes of flexible block, pin locations of all the blocks. Blocks w/ areas Block locations (shapes) netlist netlist Routing Partitioning Floorplanning/Placement (/Pin assignment)

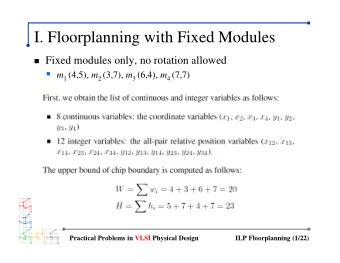

Floorplanning • Inputs to the floorplanning problem: – A set of blocks, fixed or flexible. – Pin locations of fixed blocks. – A netlist. • Objectives: Minimize area , reduce wirelength for (critical) nets, max- imize routability , determine shapes of flexible blocks 7 5 5 7 3 4 6 6 4 2 3 1 1 2 An optimal floorplan, A non−optimal floorplan in terms of area

Floorplan Design x Modules: y Area: A=xy g e Aspect ratio: r <= y/x <= s d Rotation: f Module connectivity b a 2 c b a 3 3 6 1 d c 5 5 2 f e

Floorplanning: Terminology • Rectangular dissection: Subdivision of a given rectangle by a finite # of horizontal and vertical line segments into a finite # of non-overlapping rectangles. • Slicing structure: a rectangular dissection that can be obtained by repetitively subdividing rectangles horizontally or vertically. • Slicing tree: A binary tree, where each internal node represents a vertical cut line or horizontal cut line, and each leaf a basic rectangle. • Skewed slicing tree: One in which no node and its right child are the same. V V 3 3 H H H H 1 1 5 4 2 1 H 3 2 1 V 5 4 H V V 2 V 6 7 3 2 7 6 6 7 6 7 4 5 4 5 Another slicing tree A slicing tree (skewed) Slicing floorplan Non−slicing floorplan (non−skewed)

Floorplan Design by Simulated Annealing • Related work – Wong & Liu, “A new algorithm for floorplan design,” DAC’86. ∗ Consider slicing floorplans. – Wong & Liu, “Floorplan design for rectangular and L-shaped mod- ules,” ICCAD’87. ∗ Also consider L-shaped modules. – Wong, Leong, Liu, Simulated Annealing for VLSI Design, pp. 31–71, Kluwer academic Publishers, 1988. • Ingredients: solution space, neighborhood structure, cost function, an- nealing schedule?

Partitioning Sim ulated Annealing Algorithm � Concept analogous to the annealing pro cess used for metals and glass� A random initial partition is a v ailable as input� � A new partitioning is generated b y � exc hanging some elemen ts� � If the partitions impro v e the mo v e � is alw a ys accepted� � If not then the mo v e is accepted with a probabilit y whic h decreases with the increase in a parameter called temp erature T ���� j c Sherw ani �� A lgorithms for VLSI Physic al Design A utomation

Partitioning The Annealing curv e Temp Local Minima’s Global Minima Time ���� j c Sherw ani �� A lgorithms for VLSI Physic al Design A utomation

Partitioning Sim ulated Annealing Algorithm SA Algorithm b egin � � t t � � t � cur par t ini par � SCORE� cur t �� cur scor e par rep eat rep eat comp � � SELECT� par t ��� comp � � SELECT� par t ��� � EX CHANGE� comp � � comp � � t �� tr ial par t cur par tr ial scor e � SCORE� tr ial par t �� � s � tr ial scor e cur scor e � � if � � s � �� then � cur scor e � tr ial scor e � cur par t � MO VE� comp � � comp ��� else � RANDOM�� � ��� r � s if � r � e � then � t cur scor e � tr ial scor e � cur par t � MO VE� comp � � comp � �� �equilibrium at is reac hed� un til t � �� � � � �� t �t � � �freezing p oin t is reac hed� un til end� ���� j c Sherw ani �� A lgorithms for VLSI Physic al Design A utomation

Solution Representation • An expression E = e 1 e 2 . . . e 2 n − 1 , where e i ∈ { 1 , 2 , . . . , n, H, V } , 1 ≤ i ≤ 2 n − 1, is a Polish expression of length 2 n − 1 iff 1. every operand j , 1 ≤ j ≤ n , appears exactly once in E ; 2. ( the balloting property ) for every subexpression E i = e 1 . . . e i , 1 ≤ i ≤ 2 n − 1, #operands > #operators. 1 6 H 3 5 V 2 H V 7 4 H V # of operands = 4 ....... = 7 # of operators = 2 ....... = 5 • Polish expression ← → Postorder traversal. • ijH : rectangle i on bottom of j ; ijV : rectangle i on the left of j . V 7 5 H H 4 V V 3 4 6 H 2 7 5 2 1 6 3 1 E = 16H2V75VH34HV E = 16+2*75*+34+* Postorder traversal of a tree!

Solution Representation (cont’d) V V V 3 V 1 4 H 1 4 4 H 1 2 3 3 2 2 E = 123H4VV E = 123HV4V non−skewed! skewed! H V Non−skewed V H cases ....... HH ........ ....... VV ........ • Question: How to eliminate ambiguous representation?

Normalized Polish Expression • A Polish expression E = e 1 e 2 . . . e 2 n − 1 is called normalized iff E has no consecutive operators of the same type ( H or V ). • Given a normalized Polish expression, we can construct a unique rect- angular slicing structure. V 7 5 H H 4 V V 3 4 6 H 2 7 5 2 1 6 3 1 E = 16H2V75VH34HV A normalized Polish expression

Neighborhood Structure • Chain: HV HV H . . . or V HV HV . . . 1 6 H 3 5 V 2 H V 7 4 H V chain • Adjacent: 1 and 6 are adjacent operands; 2 and 7 are adjacent operands; 5 and V are adjacent operand and operator. • 3 types of moves: – M 1 (Operand Swap) : Swap two adjacent operands. – M 2 (Chain Invert) : Complement some chain ( V = H, H = V ). – M 3 (Operator/Operand Swap) : Swap two adjacent operand and operator.

Effects of Perturbation 3 4 2 2 4 3 3 4 4 1 2 1 1 1 2 M2 M3 M1 3 12V4H3V 12H3H4V 12H34HV 12V3H4V • Question: The balloting property holds during the moves? – M 1 and M 2 moves are OK. – Check the M 3 moves! Reject “illegal” M 3 moves. • Check M 3 moves: Assume that the M 3 move swaps the operand e i with the operator e i +1 , 1 ≤ i ≤ k − 1. Then, the swap will not violate the balloting property iff 2 N i +1 < i . – N k : # of operators in the Polish expression E = e 1 e 2 . . . e k , 1 ≤ k ≤ 2 n − 1.

Cost Function • Φ = A + λW . – A : area of the smallest rectangle – W : overall wiring length – λ : user-specified parameter 3 4 2 2 4 3 3 4 4 1 2 1 2 1 1 M2 M3 M1 3 A: 12H34HV • W = � ij c ij d ij . – c ij : # of connections between blocks i and j . – d ij : center-to-center distance between basic rectangles i and j .

Area Computation 2 1 2 { (5,5) (9,4) } V 2 5 6 2 { (3,5) (6,,4) } { (2,5) (3,4) } H H { (6,2) (3,3) } { (3,2) } V V 1 3 4 3 1 2 5 6 { (2,3) (3,2) } { (2,2) } { (1,2) (2,1) } { (2,2) } 4 3 { (1,3) (3,1) } { (2,3) (3,2) } u2 max{u1, u2} V u1 w v+w v H H V V u2 1 2 u1+u2 6 u2 5 u1 u1 4 3 v w max{v, w} • Wiring cost?

Incremental Computation of Cost Function • Each move leads to only a minor modification of the Polish expression. • At most two paths of the slicing tree need to be updated for each move. V V H H H H M1 V V V V 1 2 1 2 6 5 6 4 3 3 4 5 E = 12H34V56VHV E = 12H35V46VHV

Incremental Computation of Cost Function (cont’d) H V H H V H M2 V V V H 1 2 1 2 5 6 6 5 4 3 3 4 E = 12H34V56VHV E = 12H34V56HVH V V H 1 H H M3 V V V V 1 2 5 6 6 5 4 3 H 4 2 3 E = 12H34V56VHV E = 123H4V56VHV

Annealing Schedule • Initial solution: 12 V 3 V . . . nV . n 1 2 3 • T i = r i T 0 , i = 1 , 2 , 3 , . . . ; r = 0 . 85. • At each temperature, try kn moves ( k = 5–10). • Terminate the annealing process if – # of accepted moves < 5%, – temperature is low enough, or – run out of time.

Algorithm: Simulated Annealing Floorplanning( P, ǫ, r, k ) 1 begin 2 E ← 12 V 3 V 4 V . . . nV ; /* initial solution */ 3 Best ← E ; T 0 ← ∆ avg ln ( P ) ; M ← MT ← uphill ← 0 ; N = kn ; 4 repeat MT ← uphill ← reject ← 0 ; 5 repeat 6 7 SelectMove( M ); 8 Case M of Select two adjacent operands e i and e j ; NE ← Swap ( E, e i , e j ) ; 9 M 1 : Select a nonzero length chain C ; NE ← Complement ( E, C ) ; 10 M 2 : M 3 : done ← FALSE ; 11 while not ( done ) do 12 Select two adjacent operand e i and operator e i +1 ; 13 if ( e i − 1 � = e i +1 ) and (2 N i +1 < i ) then done ← TRUE ; 14 15 NE ← Swap ( E, e i , e i +1 ) ; MT ← MT + 1 ; ∆ cost ← cost ( NE ) − cost ( E ) ; 16 − ∆ cost if (∆ cost ≤ 0) or ( Random < e ) 17 T then 18 if (∆ cost > 0) then uphill ← uphill + 1 ; 19 E ← NE ; 20 if cost ( E ) < cost ( best ) then best ← E ; 21 else reject ← reject + 1 ; 22 23 until ( uphill > N ) or ( MT > 2 N ) ; 24 T = rT ; /* reduce temperature */ ( reject 25 until > 0 . 95) or ( T < ǫ ) or OutOfTime ; MT 26 end

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.