Design and Architectures for Embedded Systems Prof. Dr. J. Henkel - PowerPoint PPT Presentation

Design and Architectures for Embedded Systems Prof. Dr. J. Henkel Henkel Prof. Dr. J. CES - - Chair for Embedded Systems Chair for Embedded Systems CES University of Karlsruhe Karlsruhe, Germany , Germany University of Today: Embedded

Design and Architectures for Embedded Systems Prof. Dr. J. Henkel Henkel Prof. Dr. J. CES - - Chair for Embedded Systems Chair for Embedded Systems CES University of Karlsruhe Karlsruhe, Germany , Germany University of Today: Embedded Processor Platforms Today: Embedded Processor Platforms http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

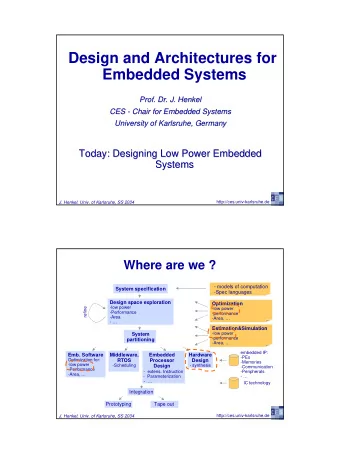

Where are we ? - models of computation System specification -Spec languages Design space exploration Optimization -low power refine -low power -Performance -performance -Area -Area, … - … Estimation&Simulation -low power System -performance partitioning -Area, … embedded IP: Emb. Software Middleware, Embedded Hardware -PEs Optimization for: RTOS Processor Design -Memories -low power -Scheduling Design - synthesis -Communication -Performance - extens. Instruction -Peripherals -Area, … - Parameterization - … - … IC technology Integration Prototyping Tape out http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Outline � Intro � Intro � Platforms � Platforms � LisaTek � LisaTek ( ( CoWare CoWare) ) � Tensilica � Tensilica’ ’s s Xtensa Xtensa � Improv � Improv � ARC � ARC � HP � HP’ ’s s PiCo PiCo � … � … others others http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

http://ces.univ-karlsruhe.de Platforms J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Designing an embedded Processor: tasks Designing SW Architectural Develop. Tools Exploration Integration and Implementing the Verification Architecture � Tasks are interdependent � Tasks are interdependent � Improvement through iteration � Improvement through iteration � Each task is customized for one specific implementation of an em � Each task is customized for one specific implementation of an embedded bedded processor processor � Many steps are manual since it is a one � Many steps are manual since it is a one- -time effort time effort � But product life times are short: can these tasks be combined an � But product life times are short: can these tasks be combined and automated d automated ? ? http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Designing an embedded Processors: the alternative way Embedded Processor Tool-suite Iterative Improvement Designing SW Architectural Develop. Tools Exploration Integration and Implementing the Verification Architecture � � There is only one generic tool There is only one generic tool- -suite that generates all other parts: suite that generates all other parts: - -> a) min. manual > a) min. manual support b) higher flexibility c) re- -use for next use for next- -gen gen embedded processor embedded processor support b) higher flexibility c) re � � Iterative improvement is done without manually re- -designing the tools designing the tools Iterative improvement is done without manually re http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Designing a customized embedded processor: approaches � � Instruction set: Instruction set: � Fully customized instructions (no predefined); but the instructi � Fully customized instructions (no predefined); but the instruction set might be on set might be domain- -specific (e.g. DSP specific (e.g. DSP- -type) type) domain � Core instruction set is fixed; the instruction set can be enhanc � Core instruction set is fixed; the instruction set can be enhanced: ed: � The � The “ “bottlenecks bottlenecks” ” of an application are hard of an application are hard- -wired as application wired as application- -specific specific instructions (might be re- -used, e.g. FFT, but might be specific to one used, e.g. FFT, but might be specific to one instructions (might be re application only); tool- -suite provides a language to do define these suite provides a language to do define these application only); tool instructions instructions � � Processor components: Processor components: � The basic (general) core can be enhanced by pre � The basic (general) core can be enhanced by pre- -defined, fixed, specialized cores: defined, fixed, specialized cores: e.g. a DSP core e.g. a DSP core � � System components (to be added/omitted and parameterized): System components (to be added/omitted and parameterized): � A) on � A) on- -chip cache: size, policy, chip cache: size, policy, … … � B) MMU � B) MMU � C) � C) … … � � On- -Chip communication infrastructure: Chip communication infrastructure: On � Busses and hierarchy of buses (processor core, inter � Busses and hierarchy of buses (processor core, inter- -core, peripheral) core, peripheral) - -> > typically typically fixed fixed http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

The LisaTek Platform\ (LisaTek: TH Aachen) � Overview � Overview � Paradigm � Paradigm � The LISA language � The LISA language � Design Flow and Tools � Design Flow and Tools � Simulation � Simulation http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Paradigm and Features � Combining architectural exploration and � Combining architectural exploration and implementation in one tool suite implementation in one tool suite � Software development tools are derived (generated) � Software development tools are derived (generated) from the description from the description � Not using a standard core; instead, the whole � Not using a standard core; instead, the whole Instruction Set Architecture (ISA) is customized Instruction Set Architecture (ISA) is customized � Status: commercial product � Status: commercial product http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Features at a glance Textual description of target architecture � Hardware Model � � Behavior : C/C+ + description � Resources : register, pipelines etc. � Timing information � Pipeline-model Software Model � � Instruction-set description Hierarchical description style � � LISA operations Different levels of abstraction � � abstraction of time (instruction/ cycle accurate) � abstraction of architecture http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Tools and Models � � Memory model Memory model I nstruction-set model � � registers, memories � � composed of valid HW registers, memories operations � bit widths, ranges � bit widths, ranges � assembly syntax � instruction word coding � � Resource model Resource model � instruction semantics � hardware resources � hardware resources Timing model � resource requirements � � resource requirements � activation sequence of of operations operations of hardware operations � pipeline � � Behavioral Model Behavioral Model � abstracted hardware � abstracted hardware Micro-architecture model � activities (various activities (various � RTL accurate hardware behavior levels) levels) � hardware operation � changing the system � changing the system (source: LISATek) grouping state state http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

LISA language: features � � Basic idea: Basic idea: closing gap between structural oriented languages (HDL, closing gap between structural oriented languages (HDL, Verilog Verilog) and ) and instruction set languages instruction set languages � � Memory model: Memory model: � registers, memories with width ranges etc. � registers, memories with width ranges etc. � � Resource model: Resource model: � � specifies available hardware (like specifies available hardware (like FUs FUs, , … …) ) � � Instruction set model: Instruction set model: � instruction word coding, spec. of valid operands and addressing � instruction word coding, spec. of valid operands and addressing modes; written modes; written in assembly syntax in assembly syntax � � Behavioral model: Behavioral model: � abstraction of hardware structures; notion of state (for simulat � abstraction of hardware structures; notion of state (for simulation; abstraction ion; abstraction level can vary level can vary � � Timing model: Timing model: � � specifying the sequence of hardware operations and units specifying the sequence of hardware operations and units � � Micro- -architectural model: architectural model: Micro � grouping of hardware operations to � grouping of hardware operations to FUs FUs; describes the details of micro ; describes the details of micro- - architectural implementation of RTL components architectural implementation of RTL components http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Design Flow and Tools Target Architecture LISA Description VHDL Description Language Compiler Simulation Library Synthesis Implementation LISA C Compiler LISA Assembler Exploration Gate-level Model LISA Linker LISA Simulator � Output/Results: � Area � Output/Results: � Power � Profiling Data Consumption � Performance Data � Clock Speed http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS04/05, 2004

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.