Design and Architectures for Embedded Systems Maik Scheer Scheer ( - PowerPoint PPT Presentation

Design and Architectures for Embedded Systems Maik Scheer Scheer ( (Lehrstuhl Lehrstuhl Prof. Dr. J. Prof. Dr. J. Henkel Henkel) ) Maik CES - - Chair for Embedded Systems Chair for Embedded Systems CES University of Karlsruhe, Germany

Design and Architectures for Embedded Systems Maik Scheer Scheer ( (Lehrstuhl Lehrstuhl Prof. Dr. J. Prof. Dr. J. Henkel Henkel) ) Maik CES - - Chair for Embedded Systems Chair for Embedded Systems CES University of Karlsruhe, Germany University of Karlsruhe, Germany Today: Reconfigurable Computing Today: Reconfigurable Computing http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

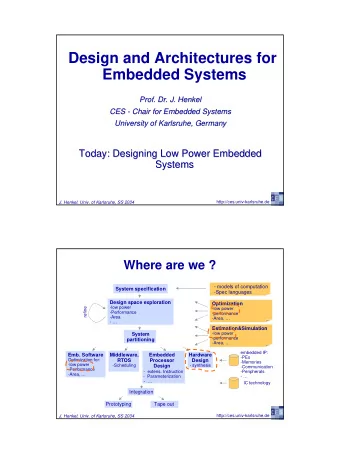

Where are we ? - models of computation System specification -Spec languages Design space exploration Optimization -low power refine -low power -Performance -performance -Area -Area, … - … Estimation&Simulation -low power System -performance partitioning -Area, … embedded IP: Emb. Software Middleware, Embedded Hardware -PEs Optimization for: RTOS Processor Design -Memories -low power -Scheduling - synthesis Design -Communication -Performance - extens. Instruction -Peripherals -Area, … - Parameterization - … - … IC technology Integration Prototyping Tape out http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Outline � Computation in Hardware vs. Computation in Software � Computation in Hardware vs. Computation in Software � Reconfigurable Computing � Reconfigurable Computing � Technologies for (Re) � Technologies for (Re)- -Configurable Hardware Configurable Hardware � Granularity � Granularity � Fine � Fine- -grained (Re) grained (Re)- -Configurable Hardware Configurable Hardware � PLDs � PLDs � FPGAs � FPGAs � Coarse � Coarse- -grained Reconfigurable Hardware grained Reconfigurable Hardware � � XPP XPP � � Dynamically Reconfigurable Dynamically Reconfigurable SoC SoC Based on LEON + XPP Based on LEON + XPP � Multi � Multi- -grained Reconfigurable Hardware grained Reconfigurable Hardware � HoneyComb � HoneyComb http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Computation in Software � NOR � NOR- -function with 8 input signals in software function with 8 input signals in software � 8 inputs at address 0x1000 � 8 inputs at address 0x1000 � Output at bit 0 of address 0x2000 � Output at bit 0 of address 0x2000 #define INPORT_ADR 0x1000 #define OUTPORT_ADR 0x2000 unsigned char *a = INPORT_ADR; unsigned char *b = OUTPORT_ADR; main() { while(1) { if(*a == 0) *b = 1; else *b = 0; } } http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Computation in Software � Assembly � Assembly- -code of the NOR code of the NOR- -function (RISC) function (RISC) � Minimum 6 cycles for computation (ELSE) � Minimum 6 cycles for computation (ELSE) � Maximum 7 cycles for computation (IF) � Maximum 7 cycles for computation (IF) � Input changes are provided to the output in minimum 5, maximum 1 � Input changes are provided to the output in minimum 5, maximum 12 2 cycles cycles L0: MOV R1, #a ; Address of a MOV R2, #b ; in R1, of b in R2 L1: LD R3, (R1) ; Inport-Bits in R3 CMP R3, #0 ; IF-condition BNE L3 L2: MOV R4, #1 ; IF-branch JMP L4 L3: MOV R4, #0 ; ELSE-branch L4: ST (R2), R4 JMP L1 http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Computation in Hardware � NOR � NOR- -function with 8 input signals in hardware function with 8 input signals in hardware � Computation time depends on propagation delay time � Computation time depends on propagation delay time � Computation time is constant and predictable � Computation time is constant and predictable Inport_0 Inport_0 Inport_1 Inport_1 Inport_2 Inport_2 Inport_3 Inport_3 ≥ 1 Outport_0 & Outport_0 Inport_4 Inport_4 Inport_5 Inport_5 Inport_6 Inport_6 Inport_7 Inport_7 http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Computation in Hardware vs. Computation in Software � Software � Software � Computation time depends on algorithm + available instruction se � Computation time depends on algorithm + available instruction set t � � Computation time can vary depending on the actual program path Computation time can vary depending on the actual program path � New algorithms can be implemented as software functions � New algorithms can be implemented as software functions � Available � Available instruction instruction set set is is fix fix � � Used silicon area is fix Used silicon area is fix � Hardware � Hardware � Each algorithm is implemented in hardware � Each algorithm is implemented in hardware � � Modifications of algorithms are not possible Modifications of algorithms are not possible � Computation time depends on critical path � Computation time depends on critical path � No fixed instruction set � No fixed instruction set � Used silicon area depends on the number of implemented � Used silicon area depends on the number of implemented instructions (algorithms) and on the instructions itself instructions (algorithms) and on the instructions itself http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Computation in Space vs. Computation in Time � Computation � Computation � � Computation in time in time Computation in in space space � Dimension of � Dimension of � � Dimension of algrithms algrithms is is time time Dimension of algorithms algorithms is is space ( space (silicon silicon area area) ) � Complex � Complex algorithms algorithms needs needs less less � Complex � computation time computation time than than simple simple Complex algoritms algoritms requires requires ones more silicon silicon area area than than simple simple ones more ones ones Algorithm is implemented during: Design time Computation time (hardware) (software) Computation is distributed in: Reconfigurable Space ASIC computing General purpose Time processor http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Reconfigurable Computing � Definition � Definition � Reconfigurable � Reconfigurable computing computing involves involves chips chips or or systems systems capable capable of of modifying themselves modifying themselves on on the the fly fly , , while while running running , to , to meet meet different different application needs needs. . application ASIC Performance Reconfigurable computing CPU‘s & DSP‘s Flexibility http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Reconfigurable Computing (cont‘d) � Pros � Pros � High � High computation computation power power ( (near near ASIC) ASIC) � Better � Better ratio ratio between between power power consumption consumption and and computing computing power power compared to to general general purpose purpose processors processors compared � Flexible � Flexible like like general general purpose purpose processors processors � Suitible � Suitible for for data data- -flow flow oriented oriented algorithms algorithms � Cons � Cons � � Reconfiguration Reconfiguration overhead overhead � Utilization � Utilization of of hardware hardware may may be be low low, , depending depending on on actual actual configuration configuration � Difficult � Difficult to to map map control control- -flow flow dominant dominant structures structures http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Technologies for Configurable Hardware � Fuse � Fuse- -Technology Technology � Silicon bridges can be destroyed through current � Silicon bridges can be destroyed through current � � One time programmable One time programmable � Anti � Anti- -Fuse Fuse- -Technology Technology � Two metal layers with dielectric in between (capacitor) � Two metal layers with dielectric in between (capacitor) � � High resistance when not programmed High resistance when not programmed � Dielectric layer can be destroyed through high voltage � Dielectric layer can be destroyed through high voltage - -> The metal > The metal layers are connected layers are connected � One time programmable � One time programmable � Floating � Floating- -Gate Gate- -Technology (EPROM) Technology (EPROM) � CMOS � CMOS- -transistor with isolated gate transistor with isolated gate � High voltage tunnels electrons to the gate � High voltage tunnels electrons to the gate � � Deletion is done through UV Deletion is done through UV- -light light � About 100 times reprogrammable � About 100 times reprogrammable http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Technologies for Configurable Hardware � EEPROM � EEPROM- -Technology / Flash Technology / Flash- -Technology Technology � Same technique as EPROM � Same technique as EPROM � Deletion is done electrically � Deletion is done electrically � About 10.000 times reprogrammable � About 10.000 times reprogrammable � SRAM � SRAM- -Technology Technology � � Flip Flip- -Flops are used for storage Flops are used for storage � Stored configuration / data is lost when system is powered down � Stored configuration / data is lost when system is powered down � - � -> External memory needed to store configuration > External memory needed to store configuration � Unlimited times programmable � Unlimited times programmable http://ces.univ-karlsruhe.de M. Scheer, Univ. of Karlsruhe, WS04/05, 2005

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.