Design and Architectures for Embedded Systems Prof. Dr. J. Henkel - PowerPoint PPT Presentation

Design and Architectures for Embedded Systems Prof. Dr. J. Henkel Henkel Prof. Dr. J. CES - - Chair for Embedded Systems Chair for Embedded Systems CES University of Karlsruhe Karlsruhe, Germany , Germany University of Today: Code

Design and Architectures for Embedded Systems Prof. Dr. J. Henkel Henkel Prof. Dr. J. CES - - Chair for Embedded Systems Chair for Embedded Systems CES University of Karlsruhe Karlsruhe, Germany , Germany University of Today: Code Generation Issues for Today: Code Generation Issues for Embedded Processors Embedded Processors http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

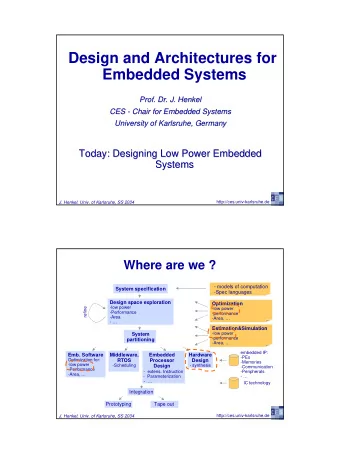

Where are we ? - models of computation System specification -Spec languages Design space exploration Optimization -low power refine -low power -Performance -performance -Area -Area, … - … Estimation&Simulation -low power System -performance partitioning -Area, … embedded IP: Emb. Software Middleware, Embedded Hardware -PEs Optimization for: RTOS Processor Design -Memories -low power -Scheduling Design - synthesis -Communication -Performance - extens. Instruction -Peripherals -Area, … - Parameterization - … - … IC technology Integration Prototyping Tape out http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Outline � Intro to code generation for embedded processors � Intro to code generation for embedded processors � Code generations approaches ( � Code generations approaches (parameterizable parameterizable) for ) for machine dependent steps: machine dependent steps: � Code selection � Code selection � Instruction scheduling � Instruction scheduling � Register allocation � Register allocation � Address code generation � Address code generation http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Retargetable Code Generation Processor Model for Source Program P Source Program P Architecture A_0 Processor Model for Compiler for Processor Architecture A_i Architecture A Retargetable Processor Model for Compiler Architecture A_n-1 Machine Code for executing P on Architecture A Machine Code for executing P on Architecture A_i � � Each processor family may have many derivates (architectural dis Each processor family may have many derivates (architectural distinctions) tinctions) � � ASIPs have three classes of parameters: have three classes of parameters: ASIPs � � Extensible instructions (user defined and completely customized) Extensible instructions (user defined and completely customized) � � Parameterizations (cache size/policy etc.) Parameterizations (cache size/policy etc.) � � In/exclusion of predefined blocks (e.g. spec purpose registers, test etc.) In/exclusion of predefined blocks (e.g. spec purpose registers, test etc.) � � => it is cumbersome to write a new compiler for each (and have t => it is cumbersome to write a new compiler for each (and have the compiler make use he compiler make use of the distinctions) => retargetable retargetable code generation techniques code generation techniques of the distinctions) => � � Note: retargetable retargetable code generation for embedded processor is different to general code generation for embedded processor is different to general- - Note: purpose purpose retargetable retargetable code generation (ex: GNU compiler) ! code generation (ex: GNU compiler) ! http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Levels of Retargetability Mainly Machine compiler Standard compiler User model supported Mainly Machine compiler Retargetable compiler Automated model process � “ � “Developer Developer Retargetability Retargetability � Parts of the compiler tool suite can be re � Parts of the compiler tool suite can be re- -used for new architecture used for new architecture but significant implementation work needs to be done but significant implementation work needs to be done � “ � “User User Retargetability Retargetability” ” � The user of the compiler tool suite can configure the compiler f � The user of the compiler tool suite can configure the compiler for or retargeting a new architecture; vendor of the tool suite does not retargeting a new architecture; vendor of the tool suite does no t need to make any changes need to make any changes http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Peculiarities of Embedded Processors w/r to Compilation � DSPs � DSPs: : � Designed for arithmetic intensive application; reoccurring � Designed for arithmetic intensive application; reoccurring algorithms and transformation like FFT etc. algorithms and transformation like FFT etc. � Dedicated hardware multipliers; � Dedicated hardware multipliers; AGUs AGUs (address generation units) (address generation units) since DSP perform memory intensive operations since DSP perform memory intensive operations � Special purpose registers: bound to certain instructions/address � Special purpose registers: bound to certain instructions/address modi modi � Some ILP (Instruction � Some ILP (Instruction- -Level Parallelism) and special reoccurring Level Parallelism) and special reoccurring instruction patterns/sequences e.g. MAC (Multiply- -and and- - instruction patterns/sequences e.g. MAC (Multiply Accumulate) Accumulate) � Architectural features make code generation quite complex � Architectural features make code generation quite complex � Major vendors: TI, Motorola, Analog Devices, NEC � Major vendors: TI, Motorola, Analog Devices, NEC http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Multi-Media Processor � Typically: VLIW (very � Typically: VLIW (very- -long long- -instruction instruction- -word) architecture word) architecture � Instruction word controls the level of parallelism that can be a � Instruction word controls the level of parallelism that can be achieved chieved � Multiple � Multiple FUs FUs operating in parallel => high peak performance operating in parallel => high peak performance � FUs � FUs not needed in a certain cycle have to be set idle (NOP) not needed in a certain cycle have to be set idle (NOP) � Optimization goal: keep � Optimization goal: keep FUs FUs busy busy � => disadvantage of � => disadvantage of VLIWs VLIWs: large code size; addressed by: : large code size; addressed by: � Code compression (like Philips � Code compression (like Philips’ ’ Trimedia Trimedia that has on that has on- -chip HW for CC) chip HW for CC) � Variable � Variable- -length VLIW: variable lengths to suppress length VLIW: variable lengths to suppress NOPs NOPs � Differential encoding: only encode diff to next VLIW instruction � Differential encoding: only encode diff to next VLIW instruction � Multiple instruction formats: (like � Multiple instruction formats: (like Infineon Infineon Carmel): dynamically Carmel): dynamically switches between 24/48/144- -bit instructions (depends on amount of bit instructions (depends on amount of switches between 24/48/144 ILP possible; done per code segment) ILP possible; done per code segment) � � Special features: Special features: � � conditional instructions (supports fast execution of if- -then then- -else) else) conditional instructions (supports fast execution of if � � SIMD (single- SIMD (single -instruction instruction- -multiple multiple- -data) instruction data) instruction � � Trimedia Trimedia TM 3260: 31 TM 3260: 31 FUs FUs (functional units); 128 general (functional units); 128 general- -purpose registers purpose registers � � Others: TI TMS320C6201 Others: TI TMS320C6201 => not as many irregularities as a ‘ ‘typical typical’ ’ DSP DSP => not as many irregularities as a � � But: many features and hence a large ‘ ‘design space design space’ ’ But: many features and hence a large http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Comparison � ASIP < � ASIP <- -> DSP/VLIW > DSP/VLIW � ASIP is designed for one specific application; DSP is designed f � ASIP is designed for one specific application; DSP is designed for or a class of applications (e.g. video processing, audio processing, , a class of applications (e.g. video processing, audio processing …) ) … � ASIP has many more degrees of freedom for configuring => large � ASIP has many more degrees of freedom for configuring => large and difficult to handle design space and difficult to handle design space � Retargetability � Retargetability is crucial for marketing modern ASIP tool suites is crucial for marketing modern ASIP tool suites � Note: � Note: � Still nowadays DSP are often programmed in assembly language � Still nowadays DSP are often programmed in assembly language (efficiency) => this is unacceptable with the rising importance of (efficiency) => this is unacceptable with the rising importance of embedded software (e.g. millions of lines of code; SW often more embedded software (e.g. millions of lines of code; SW often more costly than hardware design) costly than hardware design) � Code generation is one thing; � Code generation is one thing; efficient efficient code generation another code generation another thing thing http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, WS 04/05, 2004

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.