CPU ORGANIZATION Mahdi Nazm Bojnordi Assistant Professor School of - PowerPoint PPT Presentation

CPU ORGANIZATION Mahdi Nazm Bojnordi Assistant Professor School of Computing University of Utah CS/ECE 3810: Computer Organization Overview Notes Homework 8 is due Thursday (Mar. 28 th ) n Verify your submitted file before midnight

CPU ORGANIZATION Mahdi Nazm Bojnordi Assistant Professor School of Computing University of Utah CS/ECE 3810: Computer Organization

Overview ¨ Notes ¤ Homework 8 is due Thursday (Mar. 28 th ) n Verify your submitted file before midnight ¨ This lecture ¤ Single Cycle Processor ¤ Multi-Cycle/Pipelined Processor

Recall: Clocking the Processor ¨ Fetch unit is involved in processing all instructions ¤ Program counter (PC) and instruction memory ¨ Which of the units need a clock? ¨ What is being saved (latched) on the rising edge of the clock? ¨ The latched value remains there for an entire cycle

R-type Instructions ¨ Instructions of the form ¤ Example: add $t1, $t2, $t3 ¨ Registers and ALU

I-type Instructions ¨ Instructions of the form ¤ Examples: lw $t1, 8($t2) and sw $t1, 8($t2) ¨ Registers, ALU, and data memory ¤ Where is the constant operand

I-type Instructions ¨ Instructions of the form ¤ Examples: lw $t1, 8($t2) and sw $t1, 8($t2) ¨ Registers, ALU, and data memory ¤ Where is the constant operand

J-type Instructions ¨ Instructions of the form ¤ Example: beq $t1, $t2, offset

The Processor Datapath ¨ Control signals are generated per instruction

The Single Cycle MIPS Processor ¨ A new PC is locked at the beginning of each cycle

Processing Instructions ¨ A sequence of processing tasks per instruction

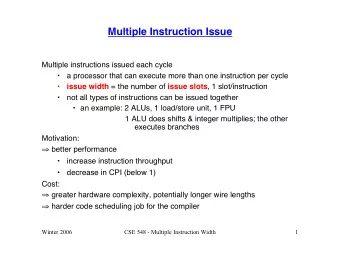

Processing Instructions ¨ Every RISC instruction may Processor require multiple processing steps functional register ¤ Instruction Fetch (IF) units file ¤ Instruction Decode (ID) ¤ Register Read (RR) n All instructions? ¤ Execute Instructions (EXE) instructions data ¤ Memory Access (MEM) n All instructions? Memory ¤ Register Write Back (WB)

Single-cycle MIPS Architecture ¨ Example: simple MIPS architecture ¤ Critical path includes all of the processing steps Write Back Controller PC Inst. Register Data ALU Memory File Memory Inst. Fetch Inst. Decode Execute Memory

Single-cycle RISC Architecture ¨ Example program ¤ CT=6ns; CPU Time = ? AND $1,$2,$3 XOR $4,$2,$3 SUB $5,$1,$4 ADD $6,$1,$4 MUL $7,$5,$6 Time

Single-cycle RISC Architecture ¨ Example program ¤ CT=6ns; CPU Time = 5 x 6ns = 30ns AND $1,$2,$3 How to improve? XOR $4,$2,$3 SUB $5,$1,$4 ADD $6,$1,$4 MUL $7,$5,$6 Time

Reusing Idle Resources ¨ Each processing step finishes in a fraction of a cycle ¤ Idle resources can be reused for processing next instructions Write Back PC Inst. Register Data ALU Memory File Memory Inst. Fetch Inst. Decode Execute Memory

Pipelined Architecture ¨ Five stage pipeline ¤ Critical path determines the cycle time 0.7ns Write Back PC Inst. Register Data ALU Memory File Memory Inst. Fetch Inst. Decode Execute Memory 1.5ns 1.05ns 1.25ns 1.5ns

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.