Chapter Five 1 2004 Morgan Kaufmann Publishers The Processor: - PowerPoint PPT Presentation

Chapter Five 1 2004 Morgan Kaufmann Publishers The Processor: Datapath & Control We're ready to look at an implementation of the MIPS Simplified to contain only: memory-reference instructions: lw, sw arithmetic-logical

Chapter Five 1 2004 Morgan Kaufmann Publishers

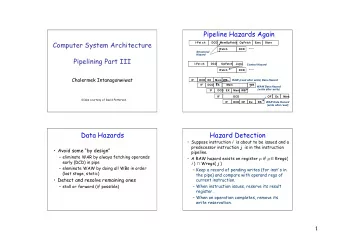

The Processor: Datapath & Control • We're ready to look at an implementation of the MIPS Simplified to contain only: • – memory-reference instructions: lw, sw – arithmetic-logical instructions: add, sub, and, or, slt – control flow instructions: beq, j • Generic Implementation: – use the program counter (PC) to supply instruction address – get the instruction from memory – read registers – use the instruction to decide exactly what to do All instructions use the ALU after reading the registers • Why? memory-reference? arithmetic? control flow? 2 2004 Morgan Kaufmann Publishers

More Implementation Details • Abstract / Simplified View: Two types of functional units: • – elements that operate on data values (combinational) – elements that contain state (sequential) 3 2004 Morgan Kaufmann Publishers

More Implementation Details • Include necessary multiplexors and control lines 4 2004 Morgan Kaufmann Publishers

State Elements • Unclocked vs. Clocked • Clocks used in synchronous logic – when should an element that contains state be updated? Falling edge Clock period Rising edge 5 2004 Morgan Kaufmann Publishers

An unclocked state element • The set-reset latch – output depends on present inputs and also on past inputs R Q Q S 6 2004 Morgan Kaufmann Publishers

Latches and Flip-flops • Output is equal to the stored value inside the element (don't need to ask for permission to look at the value) Change of state (value) is based on the clock • Latches: whenever the inputs change, and the clock is asserted • Flip-flop: state changes only on a clock edge • (edge-triggered methodology) "logically true", — could mean electrically low A clocking methodology defines when signals can be read and written — wouldn't want to read a signal at the same time it was being written 7 2004 Morgan Kaufmann Publishers

D-latch • Two inputs: – the data value to be stored (D) – the clock signal (C) indicating when to read & store D • Two outputs: – the value of the internal state (Q) and it's complement C D Q C Q _ Q D 8 2004 Morgan Kaufmann Publishers

D flip-flop • Output changes only on the clock edge Q Q D D D Q D D latch latch Q C C Q C D C Q 9 2004 Morgan Kaufmann Publishers

Our Implementation • An edge triggered methodology • Typical execution: – read contents of some state elements, – send values through some combinational logic – write results to one or more state elements 10 2004 Morgan Kaufmann Publishers

Register File • Built using D flip-flops Do you understand? What is the “Mux” above? 11 2004 Morgan Kaufmann Publishers

Register File • Note: we still use the real clock to determine when to write 12 2004 Morgan Kaufmann Publishers

Building a Datapath Datapath: • – For fetching instrs and incrementing the PC – For R-type (or arithmetic-logical) instrs – For MIPS load & store instrs – For the beq instr – For the jump ( j ) instr • • Instruction formats: Instruction formats: Name Fields Comments Field size 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits All MIPS instructions 32 bits R-format op rs rt rd shamt funct Arithmetic instructions format I-format op rs rt address/immediate Transfer, branch, imm. format J-format op target address Jump instruction format 13 2004 Morgan Kaufmann Publishers

Building a Datapath: Fetching instrs and incrementing PC • Operations: – To execute any instr: fetch the instr from memory – To prepare for the next instr: increment the PC (4 bytes later) • The datapath elements: two state elements and an adder • state elements: to store and access instructions, • adder: to compute the next instruction address. 14 2004 Morgan Kaufmann Publishers

Building a Datapath: Fetching instrs and incrementing PC • A portion of the datapath used for fetching instrs and increment PC: 15 2004 Morgan Kaufmann Publishers

Building a Datapath: R-type (arithmetic-logical) instrs Instrs included: add , sub , and , or , slt • – E.g.: add $t1, $t2, $t3 # t1 = t2 + t3 • Operations: (assume that the instr has already been fetched) Read two regs, perform an ALU op on the contents of the regs, & write the result. • The datapath elements: register file and ALU. 16 2004 Morgan Kaufmann Publishers

Building a Datapath: R-type ( arithmetic-logical ) instrs • The datapath for R-type instrs ( add ): ALU operation Read � 3 register 1 Read � data 1 Read � Zero register 2 Instruction Registers Registers ALU ALU ALU � � Write � result register Read � data 2 Write � data RegWrite 17 2004 Morgan Kaufmann Publishers

Building a Datapath: load and store instrs • Instrs included: lw , sw E.g.s: lw $t1, offset_value($t2) sw $t1, offset_value($t2) – Ops: (assume that the instr has already been fetched) • – Compute a mem addr by adding the base reg ($t2) to the 16-bit signed, offset field contained in the instr. – For sw , the value to be stored must be read from the reg file ($t1). For lw , the value read from mem must be written to the reg file ($t1). – The datapath elements: data memory unit and sign extension unit (in • addition to register file and ALU for R-type instr.) 18 2004 Morgan Kaufmann Publishers

Building a Datapath: load and store instrs • The datapath for a load or store: ALU operation 3 Read � register 1 MemWrite Read � data 1 Read � Zero register 2 Instruction ALU ALU � Registers Read � Write � result Address data register Read � data 2 data 2 Write � Write � Data � data memory Write � RegWrite data 16 32 Sign � MemRead extend FIGURE: The datapath for a load or store does a register access, followed by a memory address calculation, then a read or write from memory, and a write into the register file if the instruction is a load. 19 2004 Morgan Kaufmann Publishers

Building a Datapath: beq instr • Branch instr: – E.g. : beq $t1, $t2, offset# if ($t1 = $t2) go to PC+4+(4 × × offset) × × • Ops: (assume that the instr has already been fetched) i. Compute the branch target address: PC ← ← PC+4+(4 × × offset) ← ← × × ii. Compare the reg contents: If the condition is true, the branch target addr becomes the • new PC. new PC. • Otherwise, the incremented PC replaces the current PC. 20 2004 Morgan Kaufmann Publishers

Building a Datapath: beq instr • The datapath for a branch ( beq ): FIGURE 5.9 The datapath for a branch uses the ALU to evaluate the branch evaluate the branch condition and a separate adder to compute the branch target as the sum of the incremented PC and the sign-extended, lower 16 bits of the instruction (the branch displacement), shifted left 2 bits. 21 2004 Morgan Kaufmann Publishers

Building a Datapath: jump (j) instr • The jump instr: – E.g.: j offset # go to offset • Ops: – Replace a portion of the PC with the lower 26 bits of the instr shifted left by 2 bits (i.e., concatenating 00 to the jump offset). 22 2004 Morgan Kaufmann Publishers

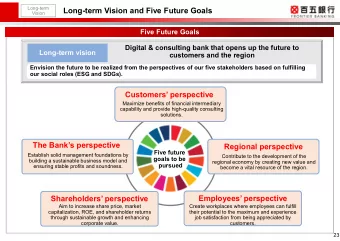

Two different implementations The implementations: • i. a simple implementation (Single Cycle implementation) ii. a multicycle implementation 23 2004 Morgan Kaufmann Publishers

A Simple Implementation Scheme (p.298) The simple implementation (Single Cycle Approach): • – the MIPS subset: lw , sw , add , sub , and , or , slt , beq – uses a single clock cycle for every instr: • no datapath resource can be used more than once per instr • any element needed more than once must be duplicated • need a mem for instrs separate from one for data – The sharing of a datapath element: multiplexor (data selector) – The sharing of a datapath element: multiplexor (data selector) • allow multiple connections to the input of an element • have a control signal select among the inputs 24 2004 Morgan Kaufmann Publishers

How to combines these together? Instruction Load & Store fetch ALU operation Read � 3 register 1 Read � data 1 Read � Zero register 2 Instruction Registers ALU ALU � Write � result register Read � data 2 Write � data RegWrite Beq R-type 25 2004 Morgan Kaufmann Publishers

The Datapath with MUXs and Control Signals Non-branch beq R-type & lw sw sw lw lw R-type R-type lw & sw R-type lw 26 2004 Morgan Kaufmann Publishers

Simple Implementation for MIPS architecture • Figure 5.11: Use multiplexors to stitch them together PCSrc 3 Non-branch – M � Add u � x Add ALU � 4 result beq Shift � left 2 Registers Registers ALU operation ALU operation 3 rs Read � MemWrite ALUSrc Read � register 1 PC Read � address Read � rt data 1 MemtoReg Zero register 2 Instruction ALU ALU � R & beq Read � Write � Read � 2 Address � result M � data register data 2 � lw M � u � Instruction � rd u � Write � x lw & sw memory Data � x data memory Write � RegWrite 1 data 16 32 Sign � R-type MemRead extend lw rt M 4 U rd X R-type 27 2004 Morgan Kaufmann Publishers

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.