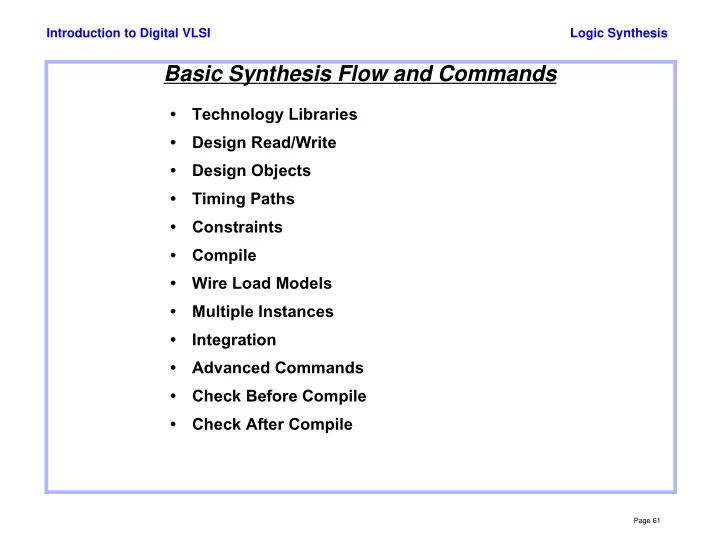

Basic Synthesis Flow and Commands Technology Libraries Design - PowerPoint PPT Presentation

Introduction to Digital VLSI Logic Synthesis Basic Synthesis Flow and Commands Technology Libraries Design Read/Write Design Objects Timing Paths Constraints Compile Wire Load Models Multiple

Introduction to Digital VLSI Logic Synthesis Basic Synthesis Flow and Commands • Technology Libraries • Design Read/Write • Design Objects • Timing Paths • Constraints • Compile • Wire Load Models • Multiple Instances • Integration • Advanced Commands • Check Before Compile • Check After Compile Page 61

Introduction to Digital VLSI Logic Synthesis Synthesis Script Flow 1. Configuration variables, e.g. bus_naming_style, verilogout_no_tri 2. Library variables 3. Read design 4. Constraints 5. Compile 6. Reports 7. Write design Page 62

Introduction to Digital VLSI Logic Synthesis Some Tcl Syntax dc_shell-t> set a 5 5 dc_shell-t> set b {c d $a [list $a z]} c d $a [list $a z] dc_shell-t> set b [list c d $a [list $a z]] c d 5 {5 z} dc_shell-t> set delay [expr .5 * $base_delay] • [ cmd ] — returns the result of the command: like ‘ cmd ‘ in csh. • {} — creates a list without variable or command substitution • Use the list command when variable and/or command subtitution is required. • Use the expr command for all arithmetic expressions. Many Tcl resources (for advanced scripts): http://tcl.activestate.com Page 63

Introduction to Digital VLSI Logic Synthesis Technology Libraries Target Library • The target library is the technology library you want to map to during synthesis. It is also known as the destination library. • Specify the target library with the pointer variable target_library . set target_library {"cdr2synPwcslV300T125.db" "scanff.db"} Optimized Netlist Design Compiler Design is mapped to gates from target_library . Target Library Page 64

Introduction to Digital VLSI Logic Synthesis Link Library • The link library is a technology library that is used to describe the function of mapped cells prior to optimization. • Specify the link library with the variable pointer link_library . • Typically, the link and target library are set to the same technology library. • The first entry in the list should be "*" to use designs currently in memory. Link Library HDL Code Optimized RTL + manually Netlist instantiated gates Design Compiler Netlist Design is mapped to gates from target_library . from earlier synthesis Target Library Page 65

Introduction to Digital VLSI Logic Synthesis Physical Technology Libraries (PC Flow) Physical Library • The physical library is the technology library which inbclues the physical design rules and physical view of the standard cells. • Specify the physical library with the pointer variable physical_library. set physical_library {"cmos090gp_h8hp_tech.pdb" "cmos090gp_h8hp_stdcells.pdb"} Link Library HDL Code RTL + manually Optimized (mapped and placed) Netlist instantiated gates Physical Compiler Netlist from earlier synthesis Design mapped to gates from target library Design placed according to physical library Target Physical Output: Verilog GLV and layout pdef/def format Library Library Floorplan Page 66

Introduction to Digital VLSI Logic Synthesis Example of Libraries include file set search_path [concat $search_path \ /usr/cad/library/udr2/synopsys_1998.02 \ ~ppcec/synopsys/lib_1998.02] set target_library { \ adv_lib_3state_udr2_85_wcs_v3t135_3c.db \ adv_lib_comb_udr2_85_wcs_v3t135_3c.db \ adv_lib_dff_udr2_85_wcs_v3t135_3c.db \ adv_lib_latch_udr2_85_wcs_v3t135_3c.db \ msil_udr2_85_wcs_v3t150.db \ ppcec_prv_udr2_85_wcs_v3t135.db \ clock_driver.db \ wire_load_models.db \ } set link_library { "*" \ adv_lib_3state_udr2_85_wcs_v3t135_3c.db \ adv_lib_comb_udr2_85_wcs_v3t135_3c.db \ adv_lib_dff_udr2_85_wcs_v3t135_3c.db \ adv_lib_latch_udr2_85_wcs_v3t135_3c.db \ adv_lib_latch_old_udr2_85_wcs_v3t135_3c.db \ msil_udr2_85_wcs_v3t150.db \ ppcec_prv_udr2_85_wcs_v3t135.db \ clock_driver.db \ wire_load_models.db \ } Page 67

Introduction to Digital VLSI Logic Synthesis Design Read read_file [ -format input_format] [-define macro_names] file_list • -format input_format • db — Synopsys internal database format (smaller and loads faster than netlist) • verilog — RTL or gate-level Verilog netlist • -define macro_names: enables setting defined values used in the Verilog source code. If you code uses ‘ifdef statements, you should set: hdlin_enable_vpp=”true” • read_db or read_verilog are equivalent to read_file -format xxx Example: read_file -format verilog -define BLOCK_A_DEF { block_a.v block_b.v } current_design [design] • returns or sets the current working design • Note: The read command sets the last module read as the current design. Page 68

Introduction to Digital VLSI Logic Synthesis Design Read by Analyze and Elaborate analyze & elaborate flow can be for power compiler clock gating, or for set- ting a parametric design selection analyze [ -format input_format] [-update] [-define macro_names] file_list • Analyzes HDL files and stores the intermediate format for the HDL description in the specified library. Similar to first stage of read_file. Example: analyze -f verilog -update { block_a.v block_b.v } elaborate top_design [ -parameters param_list] [-architecture arch_name] [-update] [-gate_clock] Example: elaborate -update mult -parameters "N=8,M=3" -gate_clock Page 69

Introduction to Digital VLSI Logic Synthesis Design Write write_file [ -format output_format] [ -hierarchy ] [ -output output_file_name] [design_list] • output_format can be db or verilog as above • -hierarchy writes the entire hierarchy from the named design down; otherwise, only the top-level module is saved • The default for design_list is the current design. Page 70

Introduction to Digital VLSI Logic Synthesis Design Objects Design module m (i1, i2, i3, i4, clk, out1); input i1, i2, i3, i4, clk; Port Net output out1; wire int1, int0; kuku U1 (.a(i1), .b(i2), .c(i3), .d(in4), .q1(int1), .q0(int0)); ind3f U2 (.IN1(int1), .IN2(int0), .IN3(clk), .OUT1(out1)); Reference endmodule Pin Cell Page 71

Introduction to Digital VLSI Logic Synthesis Design Objects (cont.) • Design : A circuit description that performs one or more logical functions (i.e Verilog module). • Cell : An instantiation of a design within another design (i.e Verilog instance). • Reference : The original design that a cell "points to" (i.e Verilog sub- module) • Port : The input, output or inout port of a Design. • Pin : The input, output or inout pin of a Cell in the Design. • Net : The wire that connects Ports to Pins and/or Pins to each other. • Clock : Port of a Design or Pin of a Cell explicitly defined as a clock source. Page 72

Introduction to Digital VLSI Logic Synthesis Design Objects Exercise INPUT1 OUTPUT1 in1 ind2c out1 D Q (i1) in2 int1 dffrpc INPUT2 (i8) C clk RB reset • all_inputs {"clk", "in1", "in2", "reset"} • all_outputs {"out1"} • all_clocks /* works only after clocks are defined */ {"clk"} • all_registers {"i8"} • all_connected int1 {"i1/OUTPUT1", "i8/D"} Page 73

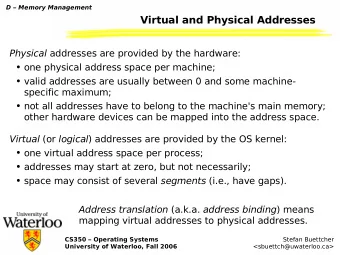

Introduction to Digital VLSI Logic Synthesis Timing Paths • Timing paths are usually: • input port -> output port • input port -> register • register -> output port • register -> register • The startpoint from a FF is the clock pin. • The endpoint at a FF is a data pin. • Timing paths do not go through FFs (except for asynchronous set/ reset). Page 74

Introduction to Digital VLSI Logic Synthesis Timing Paths Example oe clk aoi211 q d out[2:0] dffp 2 qb trinv iand2 aoi21 q d dffp 1 qb trinv aoi211 q d reset 0 dffp trinv (synnchonous) qb Page 75

Introduction to Digital VLSI Logic Synthesis Timing Path - Input Port to Output Port possible clk clock tree create_clock set_max_delay in1 set_input_delay c q d rst in2 Comb1 Comb2 out c set_output_delay q d rst rst (async) Page 76

Introduction to Digital VLSI Logic Synthesis Timing Path - Input Port to Register possible clk clock tree create_clock in1 c q d rst in2 Comb1 Comb2 out set_input_delay c q d rst rst (async) Page 77

Introduction to Digital VLSI Logic Synthesis Timing Path - Register to Output Port possible clk clock tree create_clock in1 c q d rst in2 Comb1 Comb2 out c set_output_delay q d rst rst (async) Page 78

Introduction to Digital VLSI Logic Synthesis Timing Path - Register to Register possible clk clock tree create_clock in1 c q d rst in2 Comb1 Comb2 out c q d rst rst (async) Page 79

Introduction to Digital VLSI Logic Synthesis Timing Path - Transparent Latch, Input to Output possible clk clock is active when in2 changes clock tree create_clock in1 en q d Latch rst in2 Comb1 Comb2 out set_input_delay c set_output_delay q d DFF rst rst (async) Page 80

Introduction to Digital VLSI Logic Synthesis False Timing Path - from Async Set/Reset (not checked) possible clk clock tree create_clock in1 c q d rst in2 Comb1 Comb2 out c q d rst rst (async) Page 81

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.