1 Today VM as a Tool for Caching Address spaces Conceptually, - PDF document

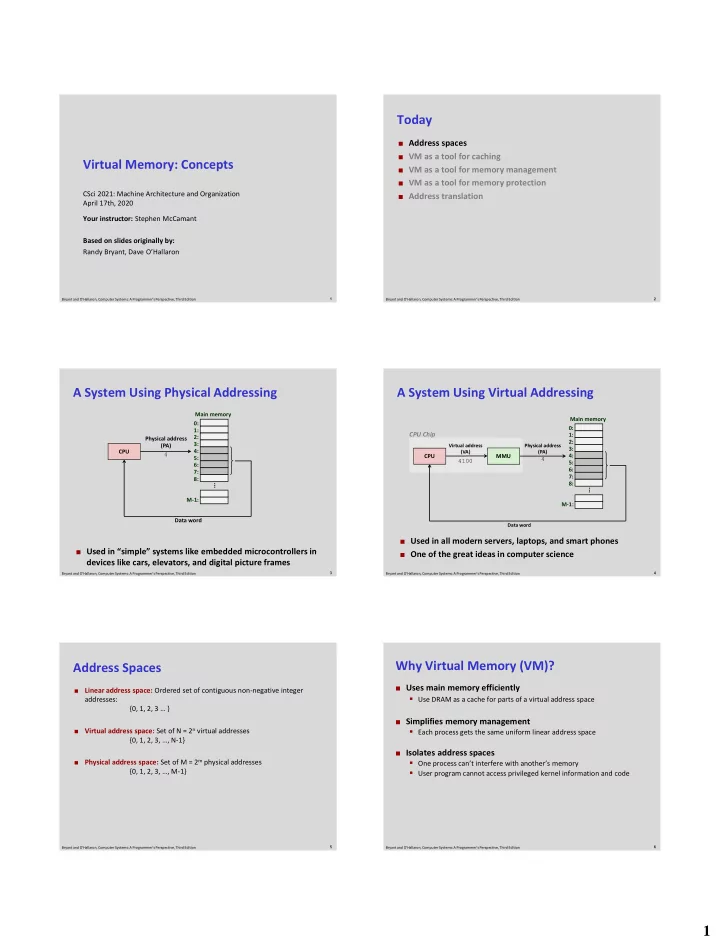

Today Address spaces VM as a tool for caching Virtual Memory: Concepts VM as a tool for memory management VM as a tool for memory protection CSci 2021: Machine Architecture and Organization Address translation April 17th, 2020

Today Address spaces VM as a tool for caching Virtual Memory: Concepts VM as a tool for memory management VM as a tool for memory protection CSci 2021: Machine Architecture and Organization Address translation April 17th, 2020 Your instructor: Stephen McCamant Based on slides originally by: Randy Bryant, Dave O’Hallaron 1 2 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition A System Using Physical Addressing A System Using Virtual Addressing Main memory Main memory 0: 0: 1: CPU Chip 1: 2: Physical address 2: 3: (PA) Virtual address Physical address 3: CPU 4: (VA) (PA) 4 4: CPU MMU 5: 4 4100 5: 6: 6: 7: 7: 8: 8: ... ... M-1: M-1: Data word Data word Used in all modern servers, laptops, and smart phones Used in “simple” systems like embedded microcontrollers in One of the great ideas in computer science devices like cars, elevators, and digital picture frames 3 4 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Why Virtual Memory (VM)? Address Spaces Uses main memory efficiently Linear address space: Ordered set of contiguous non-negative integer Use DRAM as a cache for parts of a virtual address space addresses: {0, 1, 2, 3 … } Simplifies memory management Virtual address space: Set of N = 2 n virtual addresses Each process gets the same uniform linear address space {0, 1, 2, 3, …, N -1} Isolates address spaces Physical address space: Set of M = 2 m physical addresses One process can’t interfere with another’s memory {0, 1, 2, 3, …, M -1} User program cannot access privileged kernel information and code 5 6 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition 1

Today VM as a Tool for Caching Address spaces Conceptually, virtual memory is an array of N contiguous bytes stored on disk. VM as a tool for caching The contents of the array on disk are cached in physical VM as a tool for memory management memory ( DRAM cache ) VM as a tool for memory protection These cache blocks are called pages (size is P = 2 p bytes) Address translation Virtual memory Physical memory 0 VP 0 Unallocated 0 VP 1 Cached Empty PP 0 Uncached PP 1 Unallocated Empty Cached Uncached Empty Cached PP 2 m-p -1 M-1 VP 2 n-p -1 Uncached N-1 Virtual pages (VPs) Physical pages (PPs) stored on disk cached in DRAM 7 9 Bryant and O ’ Hallaron, Computer Systems: A Programmer ’ s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Enabling Data Structure: Page Table DRAM Cache Organization A page table is an array of page table entries (PTEs) that DRAM cache organization driven by the enormous miss penalty maps virtual pages to physical pages. DRAM is about 10x slower than SRAM Per-process kernel data structure in DRAM Disk is about 10,000x slower than DRAM Physical memory Physical page (DRAM) number or VP 1 PP 0 Consequences Valid disk address VP 2 PTE 0 0 null Large page (block) size: typically 4 KB, sometimes 4 MB VP 7 1 VP 4 PP 3 Fully associative 1 0 Any VP can be placed in any PP 1 Virtual memory 0 null Requires a “ large ” mapping function – different from cache memories (disk) 0 Highly sophisticated, expensive replacement algorithms PTE 7 1 VP 1 Memory resident Too complicated and open-ended to be implemented in hardware VP 2 page table Write-back rather than write-through VP 3 (DRAM) VP 4 VP 6 VP 7 10 11 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Page Hit Page Fault Page hit: reference to VM word that is in physical memory Page fault: reference to VM word that is not in physical (DRAM cache hit) memory (DRAM cache miss) Physical memory Physical memory Physical page Physical page (DRAM) (DRAM) Virtual address Virtual address number or number or VP 1 PP 0 VP 1 PP 0 Valid disk address Valid disk address VP 2 VP 2 PTE 0 0 null PTE 0 0 null VP 7 VP 7 1 1 VP 4 PP 3 VP 4 PP 3 1 1 0 0 1 1 Virtual memory Virtual memory 0 null 0 null (disk) (disk) 0 0 PTE 7 1 PTE 7 1 VP 1 VP 1 Memory resident Memory resident VP 2 VP 2 page table page table VP 3 VP 3 (DRAM) (DRAM) VP 4 VP 4 VP 6 VP 6 VP 7 VP 7 12 13 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition 2

Handling Page Fault Handling Page Fault Page miss causes page fault (an exception) Page miss causes page fault (an exception) Page fault handler selects a victim to be evicted (here VP 4) Physical memory Physical memory Physical page Physical page (DRAM) (DRAM) Virtual address Virtual address number or number or VP 1 PP 0 VP 1 PP 0 Valid disk address Valid disk address VP 2 VP 2 PTE 0 null PTE 0 null 0 0 VP 7 VP 7 1 1 VP 4 PP 3 VP 4 PP 3 1 1 0 0 1 1 Virtual memory Virtual memory 0 null 0 null (disk) (disk) 0 0 PTE 7 1 PTE 7 1 VP 1 VP 1 Memory resident Memory resident VP 2 VP 2 page table page table VP 3 VP 3 (DRAM) (DRAM) VP 4 VP 4 VP 6 VP 6 VP 7 VP 7 14 15 Bryant and O ’ Hallaron, Computer Systems: A Programmer ’ s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Handling Page Fault Handling Page Fault Page miss causes page fault (an exception) Page miss causes page fault (an exception) Page fault handler selects a victim to be evicted (here VP 4) Page fault handler selects a victim to be evicted (here VP 4) Offending instruction is restarted: page hit! Physical memory Physical memory Physical page Physical page (DRAM) (DRAM) Virtual address Virtual address number or number or VP 1 PP 0 VP 1 PP 0 Valid disk address Valid disk address VP 2 VP 2 PTE 0 null PTE 0 null 0 0 VP 7 VP 7 1 1 VP 3 PP 3 VP 3 PP 3 1 1 1 1 0 0 Virtual memory Virtual memory 0 null 0 null (disk) (disk) 0 0 PTE 7 1 PTE 7 1 VP 1 VP 1 Memory resident Memory resident VP 2 VP 2 page table page table VP 3 VP 3 (DRAM) (DRAM) VP 4 VP 4 Key point: Waiting until the miss to copy the page to VP 6 VP 6 DRAM is known as demand paging VP 7 VP 7 16 17 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Locality to the Rescue Again! Allocating Pages Virtual memory seems terribly inefficient, but it works Allocating a new page (VP 5) of virtual memory. because of locality. Physical memory Physical page (DRAM) number or At any point in time, programs tend to access a set of active VP 1 PP 0 Valid disk address VP 2 virtual pages called the working set PTE 0 null 0 VP 7 1 Programs with better temporal locality will have smaller working sets VP 3 PP 3 1 1 0 If (working set size < main memory size) Virtual memory 0 Good performance for one process after compulsory misses (disk) 0 PTE 7 1 VP 1 Memory resident VP 2 If ( SUM(working set sizes) > main memory size ) page table VP 3 Thrashing: Performance meltdown where pages are swapped (copied) (DRAM) VP 4 in and out continuously VP 5 VP 6 VP 7 18 19 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.