+ A A 0 1 0 0 0 1 0 Sum MUX 0 1 1 Result 0 1 1 B - PowerPoint PPT Presentation

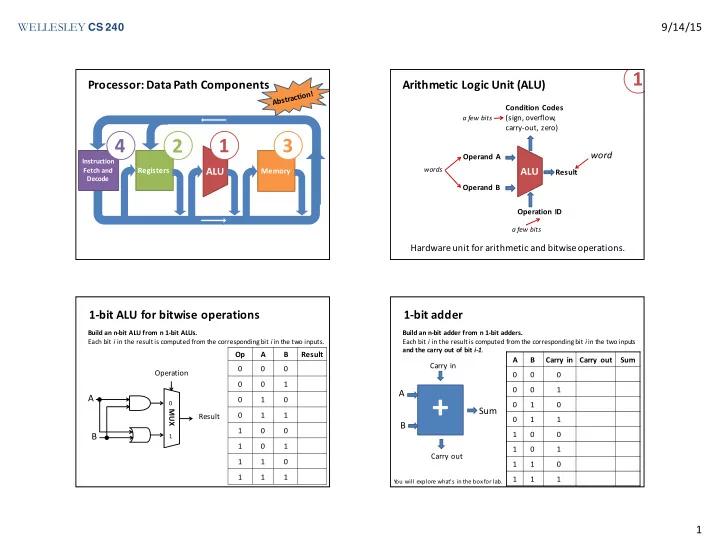

9/14/15 WELLESLEY CS 240 1 Processor: Data Path Components Arithmetic Logic Unit (ALU) Condition Codes (sign, overflow , a few bits carry-out, zero) 4 2 1 3 word Operand A

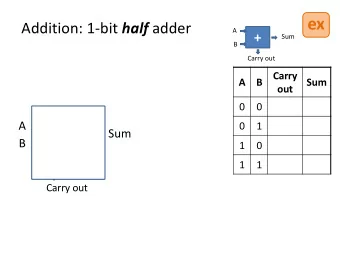

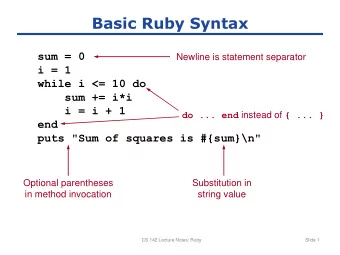

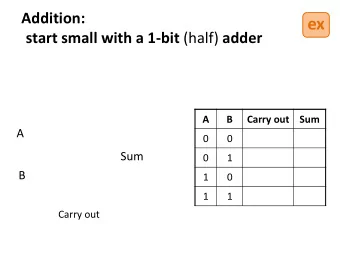

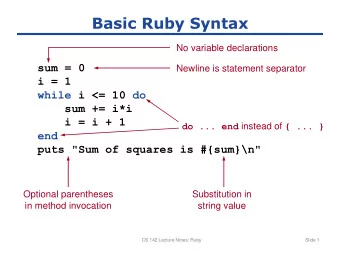

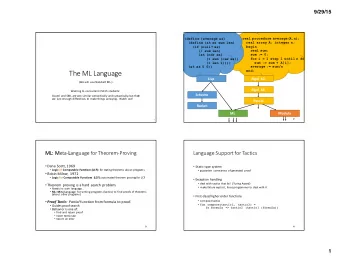

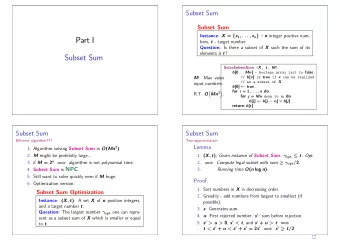

9/14/15 WELLESLEY CS 240 1 Processor: ¡Data ¡Path ¡Components Arithmetic ¡Logic ¡Unit ¡(ALU) Condition ¡Codes (sign, ¡overflow , a ¡few ¡bits carry-‑out, ¡zero) 4 2 1 3 word Operand ¡A Instruction ¡ ALU ALU Registers words Fetch and ¡ Memory Result Decode Operand ¡B Operation ¡ID a ¡few ¡bits Hardware ¡unit ¡for ¡arithmetic ¡and ¡bitwise ¡operations. 1-‑bit ¡ALU ¡for ¡bitwise ¡operations 1-‑bit ¡adder Build ¡an ¡n-‑bit ¡ALU ¡from ¡n ¡1-‑bit ¡ALUs. Build ¡an ¡n-‑bit ¡adder ¡from ¡n ¡1-‑bit ¡adders. Each ¡bit ¡ i in ¡the ¡result ¡is ¡computed ¡from ¡the ¡corresponding ¡bit ¡ i in ¡the ¡two ¡inputs. Each ¡bit ¡ i in ¡the ¡result ¡is ¡computed ¡from ¡the ¡corresponding ¡bit ¡ i in ¡the ¡two ¡inpu ts ¡ and ¡the ¡carry ¡out ¡of ¡bit ¡ i-‑1 . Op A B Result A B Carry ¡ in Carry ¡ out Sum Carry ¡in 0 0 0 Operation 0 0 0 0 0 1 0 0 1 + A A 0 1 0 0 0 1 0 Sum MUX 0 1 1 Result 0 1 1 B 1 0 0 B 1 0 0 1 1 0 1 1 0 1 Carry ¡out 1 1 0 1 1 0 1 1 1 1 1 1 Y ou ¡will ¡explore ¡what's ¡in ¡the ¡box ¡for ¡lab. 1

9/14/15 WELLESLEY CS 240 32-‑bit ¡ALU 1-‑bit ¡ALU with ¡ripple ¡carry Operation Carry ¡in 2 a 0 MUX Result 1 Sum + 2 b Carry ¡out ALU ¡Condition ¡Codes Adding ¡subtraction Zero ¡Flag: 1 ¡if ¡result ¡is ¡00...0 ¡else ¡0 Operation Sign ¡Flag: ¡ sign ¡bit ¡of ¡result Carry ¡in invert ¡B 2 A 0 Carry ¡ Flag: 1 ¡if ¡unsigned ¡overflow ¡ else ¡0 carry-‑out ¡bit ¡of ¡result MUX Result 1 Overflow ¡Flag: ¡ 1 ¡if ¡signed ¡overflow ¡ else ¡0 Sum + B 0 2 MUX 1 Carry ¡out 2

9/14/15 WELLESLEY CS 240 Compute ¡NOT, ¡NAND, ¡NOR, ¡XOR, ¡<, ¡==, ¡…? Detect ¡overflow? Controlling ¡the ¡ALU invert ¡A Operation invert ¡B Condition ¡Codes Carry ¡in ALU control ¡lines Function 2 A 0 0 0000 AND MUX Operand ¡A 1 0001 OR ALU MUX Result Result 0010 add 1 Operand ¡B 0110 subtract 1100 NOR Sum + Control ¡Lines B 0 2 MUX 1 Invert ¡A Invert ¡B Operation ¡ID Carry ¡out 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![More on Verilog Sign extension: Example 1 wire [3:0] c, d reg [4:0] sum; always @ (c or d)](https://c.sambuz.com/910046/more-on-verilog-sign-extension-example-1-s.webp)

![Problem 1 Design a Verilog 16-bit adder module module adder (A, B, sum); input [15:0] A, B;](https://c.sambuz.com/1025319/problem-1-design-a-verilog-16-bit-adder-module-module-s.webp)