7. Fundamental Transistor Amplifier Configurations Lecture notes: - PowerPoint PPT Presentation

7. Fundamental Transistor Amplifier Configurations Lecture notes: Sec. 5 Sedra & Smith (6 th Ed): Sec. 5.4, 5.6 & 6.3-6.4 Sedra & Smith (5 th Ed): Sec. 4.4, 4.6 & 5.3-5.4 ECE 65, Winter2013, F. Najmabadi Issues in developing a

7. Fundamental Transistor Amplifier Configurations Lecture notes: Sec. 5 Sedra & Smith (6 th Ed): Sec. 5.4, 5.6 & 6.3-6.4 Sedra & Smith (5 th Ed): Sec. 4.4, 4.6 & 5.3-5.4 ECE 65, Winter2013, F. Najmabadi

Issues in developing a transistor amplifier: 1. Find the iv characteristics of the elements for the signal (which can be different than their characteristics equation for bias). o This will lead to different circuit configurations for bias versus signal 2. Compute circuit response to the signal o Focus on fundamental transistor amplifier configurations 3. How to establish a Bias point (bias is the state of the system when there is no signal). o Stable and robust bias point should be resilient to variations in µ n C ox (W/L),V t (or β for BJT) due to temperature and/or manufacturing variability. o Bias point details impact small signal response (e.g., gain of the amplifier). F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (2/26)

What are amplifier parameters? v A = Voltage Gain of the Circuit : o v sig v A = o Voltage Gain of the Amplifier : v v i v = o Open - loop Gain : A vo v → ∞ i R L v R = i Input Resistance : i i i v = − Output Resistance of Amplifier : o R o i → o 0 v Output resistance is the Thevenin sig resistance between the output terminals! In general R i depends on R L and R o depends on R sig F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (3/26)

Observations on the amplifier parameters Overall Gain : v v v R = = × = o i o i A A + v v v v R R sig sig i i sig v R v R = = = i i o L A A + + v vo v R R v R R sig i sig i L o A vo is the maximum possible gain Value of R i is important. of the amplifier. o For R i >> R i , v i ≈ v sig Value of R o is important. o For R i = R sig , v i = 0.5 v sig o For R o << R L , A v ≈ A vo o For R i << R sig , v i ≈ 0 o For R o = R L , A v = 0.5 A vo Prefer “large” R i o For R o >> R L , A v ≈ 0 Prefer “small” R o F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (4/26)

Some observation on single-transistor amplifiers 1. A s we will discuss, there are many ways to bias a transistor. Thus, there are many practical single-transistor amplifier circuits. o Fortunately, signal circuits always reduce to one of four fundamental configuration . 2. We compute the voltage gain and input resistance of these four fundamental configurations in the presence of an arbitrary load R L . Then: Overall Gain : Open - loop Gain : = | v v v R A A = = × = → ∞ o i o i vo v R A A L + v v v v R R sig sig i i sig 3. R o is calculated in a real circuit (with R sig & v sig ) once load is clearly identified. F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (5/26)

Fundamental Transistor Amplifier Configurations We are considering only signal circuit here! F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (6/26)

Possible BJT amplifier configurations Common-Base Common-Emitter Common-Collector Common-Emitter with R E Same as Common Base (v i does not change) Not Useful F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (7/26)

PNP configurations are the same as those of NPN (because of similar small-signal model) Common-Emitter Common-Base Common-Collector Common-Emitter Common-Base Common-Collector F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (8/26)

MOS fundamental configurations are analogous to BJTs Common-Emitter Common-Base Common-Collector Common-Source Common-Gate Common-Drain F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (9/26)

Common Emitter Configuration Signal Circuit: Signal Circuit with BJT SSM: o r o and R’ L are in parallel o v π = v i F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (10/26)

Common Emitter Configuration ( A v & R i ) By KCL ′ = − ( || ) v v v g v r R = ⇒ = = i i o m i o L i R r π i i r i v π ′ = = − i o ( || ) A g r R v m o L v i F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (11/26)

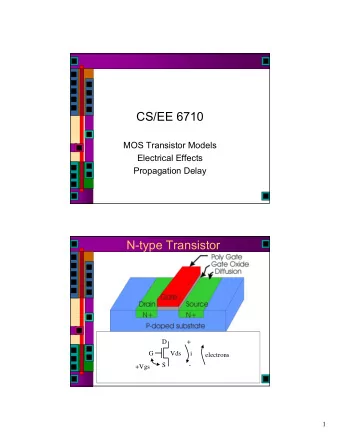

Common Source Configuration Signal Circuit: Signal Circuit with MOS SSM: o r o and R’ L are in parallel o v gs = v i F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (12/26)

Common Source Configuration ( A v & R i ) By KCL ′ = − ( || ) v v g v r R = ⇒ = = ∞ i o m i o L 0 i R i i i v ′ = = − i o ( || ) A g r R v m o L v i F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (13/26)

Common Source & Common Emitter Configurations are “similar” Signal Circuit Signal Circuit with transistor SSM v v ′ ′ = = − = = − o o ( || ) ( || ) A g r R A g r R Similar formula if v m o L v m o L → ∞ v v r we let i i π = = ∞ R r R π i i Note that A v & R i are independent of v sig & R sig F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (14/26)

Common Emitter Configuration with R E Signal Circuit: Signal Circuit with BJT SSM: F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (15/26)

Common Emitter Configuration with R E ( A v & R i ) Node voltage method : 1. Add the two node equations to get = − v v v π v e in terms of v o and v i i e − − v v v v v 2. Substitute for v e in Node v o Node v e + + − − = e e i e o ( ) 0 g v v m i e equation to find v o and gain R r r π E o 3. Compute i i in terms of node − v v v Node v o + + − = o o e ( ) 0 g v v voltages. Then R i = v i /i i ′ m i e R r L o 4. Lengthy calculations (See Notes). ′ v g R g r R = ≈ − ≈ + π o m L m E A R r π ′ ′ + + + + + v i 1 ( / )( 1 / ) 1 ( / )( 1 / ) v g R R r R r R r R r π π i m E L o E L o E F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (16/26)

Common Source Configuration with R S ( A v & R i ) Signal Circuit ′ v g R = ≈ − ′ o m L A v g R ′ = ≈ − + + + v o m L 1 ( / )( 1 / ) A v g R R r R r π ′ + + v i m E L o E 1 ( / ) v g R R r i m S L o g r R ≈ + π = ∞ m E R r R π ′ + + i i 1 ( / )( 1 / ) R r R r π L o E → ∞ r Let π → R R E S F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (17/26)

Common Base Configuration (Gain) Signal Circuit: Node voltage method: = − v v π i − v v v + + − = Node v o o o i ( ) 0 g v ′ m i R r L o + 1 v g r = o m o v Signal Circuit with BJT SSM: ′ i || r R r o L o + 1 v g r ′ = = o m o ( || ) A r R v o L v r i o ′ ≈ ( || ) A g r R v m o L F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (18/26)

Common Base Configuration ( R i ) v = i Define R x i x v v v v = + = + = KCL: i i i i i i i x || r r R r R π π π x x v = = i || R r R π i x i i ′ = + + ( ) KVL: v i g v r i R By KCL π i x m o x L = − v v π i ′ + = + ( 1 ) ( ) v g r i r R i m o x o L ′ + v r R = = i o R + x 1 i g r x m o ′ + r R = = || || o L R r R r π π + i x 1 g r m o F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (19/26)

Common Gate Configuration ( A v & R i ) Signal Circuit v v ′ ′ = ≈ = ≈ o ( || ) o ( || ) A g r R A g r R v m o L v m o L v v → ∞ i i r Let π ′ ′ + + r R r R = = || o L o L R r R π + + i i 1 1 g r g r m o m o F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (20/26)

Common Collector Configuration (Emitter Follower) Signal Circuit: Node voltage method: = − v v v π i o − v v v v Node v o + + − − = o o i o ( ) 0 g v v ′ m i o R r r π L o + + 1 1 v + = ≈ o 1 1 v g v g v ′ o m i m i || r R g r g r π π o L m m = β >> 1 g m r π Signal Circuit with BJT SSM: ′ ( || ) v g r R = = o m o L A ′ + v 1 ( || ) v g r R i m o L − v v v = = × − i o i ( 1 ) i A i v r r π π v r = = π i R − i 1 i A i v ′ ′ = + = + β ( || ) ( || ) R r g r r R r r R π π π i m o L o L F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (21/26)

Common Drain Configuration (Source Follower) Signal Circuit ′ ′ ( || ) v g r R ( || ) v g r R = = o m o L = = A o m o L A ′ + v → ∞ ′ 1 ( || ) + v g r R v r 1 ( || ) Let v g r R π i m o L i m o L = ∞ ′ ′ = = β R ( || ) ( || ) R g r r R r R i π i m o L o L F. Najmabadi, ECE65, Winter 2013, Fundamental Amp Configuration (22/26)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Transistor Channel Model [Farquhar and Hasler, 2004] Transistor HH Channel Model [Farquhar and](https://c.sambuz.com/897541/transistor-channel-model-s.webp)