Basic Single Stage Amplifier Configurations Part I Ref.: Chapter 3 - PowerPoint PPT Presentation

2 Basic Single Stage Amplifier Configurations Part I Ref.: Chapter 3 from Razavis book and chapter 3 from Grays book. IIT-Bombay Lecture 6 M. Shojaei

2 Basic Single Stage Amplifier Configurations Part I Ref.: Chapter 3 from Razavi’s book and chapter 3 from Gray’s book. IIT-Bombay Lecture 6 M. Shojaei Baghini

3 Slides Figures • Unless it’s mentioned figures and contents of slides are taken from: ‘‘Design of Analog CMOS Integrated Circuits” by Behzad Razavi IIT-Bombay Lecture 6 M. Shojaei Baghini

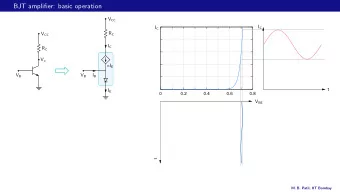

4 Common Source (CS) Amplifier with Resistive Load Subthreshold/Moderate Inversion region • Biasing using gate voltage • Concept of load line to trace large (DC or AC coupled) and signal values of voltage and current drain resistor IIT-Bombay Lecture 6 M. Shojaei Baghini

5 CS Amplifier with Resistive Load (cont’d) − V V gs TH nV R I e T D 0 ( 1 ) nV T Three different ( ) W µ − ( 2 ) C V V R Gain : operating ox gs TH D L W µ regions: ( 3 ) C V R ox DS D L ( ) < − V V V DS gs TH IIT-Bombay Lecture 6 M. Shojaei Baghini

6 CS Amplifier with Resistive Load (cont’d) − V V Subthreshold GS TH nV R I R I e T = region D D _ subthresho ld D 0 nV nV Gain : T T 2 R I W ( ) µ − = D D _ saturation C V V R − ox GS TH D L V V Saturation region gs TH Gain as a function of V DC across R Tradeoff between Av, BW, swing and power Tighter tradeoff as V DD scales down IIT-Bombay Lecture 6 M. Shojaei Baghini

7 CS Amplifier with Active Load More relaxed tradeoff between Av and swing 2 ≈ − ( ) ( A ) − λ + λ v V V gs TH I 1 M 1 Sources of nonlinearity: • λ varies as V DS swings. • “gm” varies as Vin varies. IIT-Bombay Lecture 6 M. Shojaei Baghini

8 8 CS Amplifier with Diode-connected Load ( ) ( ) W µ W g 1 g L ( ) = − = − L n m = − = − ( ) 1 1 A m 1 1 A + v W g v µ g g W g + m b 2 m m 1 2 b 2 L m 2 L p 2 2 g m 2 More linear than the CS with active load but not practical for achieving high gain. IIT-Bombay Lecture 6 M. Shojaei Baghini

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.