Wire Models Wires Professor Chris Kim University of Minnesota - PowerPoint PPT Presentation

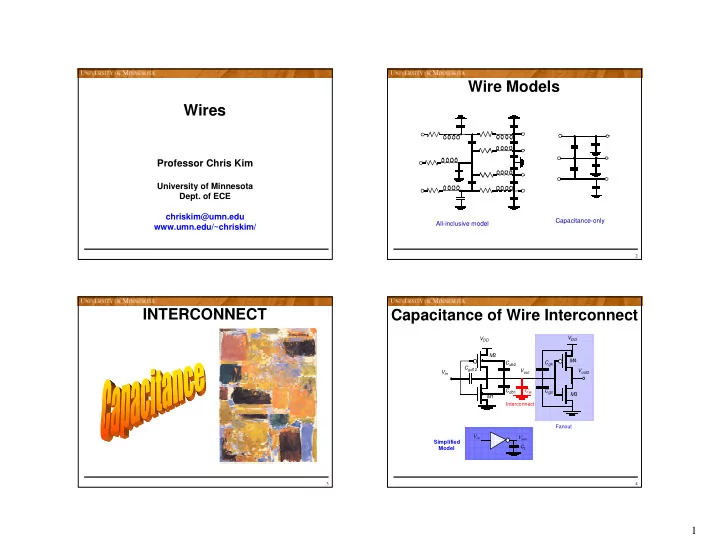

Wire Models Wires Professor Chris Kim University of Minnesota Dept. of ECE chriskim@umn.edu Capacitance-only All-inclusive model www.umn.edu/~chriskim/ 2 INTERCONNECT Capacitance of Wire Interconnect V DD V DD M 2 M 4 C db 2 C g 4 C gd 12

Wire Models Wires Professor Chris Kim University of Minnesota Dept. of ECE chriskim@umn.edu Capacitance-only All-inclusive model www.umn.edu/~chriskim/ 2 INTERCONNECT Capacitance of Wire Interconnect V DD V DD M 2 M 4 C db 2 C g 4 C gd 12 V out V out 2 V in C db 1 C w C g 3 M 3 M 1 Interconnect Fanout V in V out Simplified C L Model 3 4 1

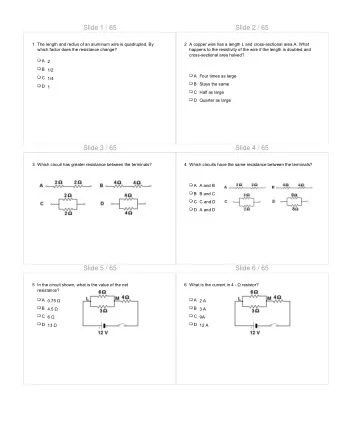

Capacitance: The Parallel Plate Model Permittivity Current flow L Electrical-field lines W H t di Dielectric Substrate ε = S 1 di c WL = = S int ⋅ Cwire t S S S di L L 5 6 Fringing Capacitance Fringing versus Parallel Plate (a) H W - H/2 + (from [Bakoglu89]) (b) 7 8 2

Interwire Capacitance Impact of Interwire Capacitance fringing parallel (from [Bakoglu89]) 9 10 INTERCONNECT Wiring Capacitances (0.25 μ m CMOS) 11 12 3

Wire Resistance Interconnect Resistance R = ρ L H W Sheet Resistance L R o H R 1 R 2 W 13 14 Dealing with Resistance Polycide Gate MOSFET • Selective Technology Scaling Silicide • Use Better Interconnect Materials PolySilicon – reduce average wire-length SiO 2 – e.g. copper, silicides n + n + • More Interconnect Layers p – reduce average wire-length Silicides: WSi 2, TiSi 2 , PtSi 2 and TaSi Conductivity: 8-10 times better than Poly 15 16 4

Sheet Resistance Modern Interconnect 17 18 Modern Interconnect Example: Intel 0.25 micron Process • 90nm process 5 metal layers Ti/Al - Cu/Ti/TiN Polysilicon dielectric 19 20 5

The Lumped Model V out c wire Driver Interconnect Interconnect Modeling Modeling R driver V out V in C lumped 21 22 The Lumped RC-Model The Elmore Delay: RC Chain The Elmore Delay 23 24 6

Wire Model The Distributed RC-line Assume: Wire modeled by N equal-length segments For large values of N: 25 26 Step-response of RC wire as RC-Models a function of time and space 2.5 x= L/10 2 x = L/4 voltage (V) 1.5 x = L/2 1 x= L 0.5 0 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 time (nsec) 27 28 7

8 29 Driving an RC-line out V ( r w ,c w ,L ) s R in V

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.