UMBC A B M A L T F O U M B C I M Y O R T 1 (April - PowerPoint PPT Presentation

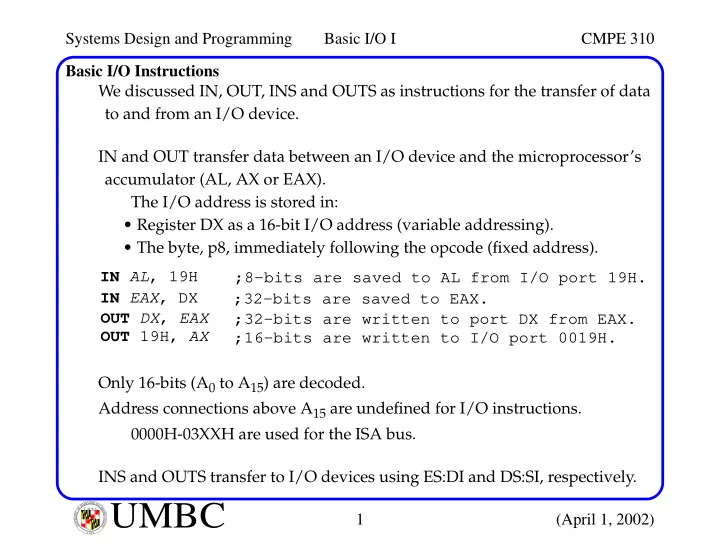

Systems Design and Programming Basic I/O I CMPE 310 Basic I/O Instructions We discussed IN, OUT, INS and OUTS as instructions for the transfer of data to and from an I/O device. IN and OUT transfer data between an I/O device and the

Systems Design and Programming Basic I/O I CMPE 310 Basic I/O Instructions We discussed IN, OUT, INS and OUTS as instructions for the transfer of data to and from an I/O device. IN and OUT transfer data between an I/O device and the microprocessor’s accumulator (AL, AX or EAX). The I/O address is stored in: • Register DX as a 16-bit I/O address (variable addressing). • The byte, p8, immediately following the opcode (fixed address). IN AL , 19H ;8-bits are saved to AL from I/O port 19H. IN EAX , DX ;32-bits are saved to EAX. OUT DX , EAX ;32-bits are written to port DX from EAX. OUT 19H, AX ;16-bits are written to I/O port 0019H. Only 16-bits (A 0 to A 15 ) are decoded. Address connections above A 15 are undefined for I/O instructions. 0000H-03XXH are used for the ISA bus. INS and OUTS transfer to I/O devices using ES:DI and DS:SI, respectively. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Isolated versus Memory-Mapped I/O Isolated and Memory-Mapped I/O: In the Isolated scheme, IN, OUT, INS and OUTS are required. In the Memory-mapped scheme, any instruction that references memory can be used. Disadvantage: Memory A portion of the memory space FFFFF is used for I/O devices. Advantage: Overlapped IORC and IOWC not required. I/O spaces Any data transfer instruction. Disadvantage: 1M X 8 Hardware using M/IO and Separate spaces W/R needed to develop signals IORC and IOWC. I/O FFFF Requires IN, OUT, INS and 64K X 8 64K X 8 00000 0000 OUTS 8-bit port addresses used to access system board device, e.g. timer and key- board. 16-bit port addresses used to access serial and parallel ports, harddrives, etc. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 I/O Map FFFF I/O Expansion Area Fixed I/O areas PCI Bus, user apps and main-board functions 0400 COM 1 03F8 Floppy disk 03F0 03E0 CGI adapter 03D0 0380 LPT 1 0378 Variable Port 0330 Hard disk I/O instuctions 0320 Computer system 0300 and ISA Bus COM 2 02F8 0064 8255(PPI) 0060 0044 Timer Fixed Port 0040 I/O instuctions 0024 Interrupt controller 0020 0010 DMA controller 0000 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Basic I/O Interface The basic input device (to the microprocessor) is a set of tri-state buffers. The basic output device (from the microprocessor) is a set of latches. Basic Input Interface: VCC When tri-states are enabled, 8-bit input port microprocessor can read Toggle switches state of toggle switches into are data source. AL (using IN instruction). 10K Ω 74ALS244 1A 1 1Y 1 1A 2 1Y 2 1A 3 1Y 3 1A 4 1Y 4 Data Bus 2A 1 2Y 1 2A 2 2Y 2 2A 3 2Y 3 2A 4 2Y 4 SEL 1G 2G I/O port address decoded to SEL L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Basic I/O Interface Basic Output Interface: VCC D flip-flops hold 330 Ω data from microprocessor U1 D 0 Q 0 D 1 Q 1 74ALS374 D 2 Q 2 Data Bus D 3 Q 3 Light-emitting D 4 Q 4 diodes emit D 5 Q 5 when Q output D 6 Q 6 is set to logic 0. D 7 Q 7 OC SEL CLK In this case, the data from the OUT instruction is latched using SEL. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

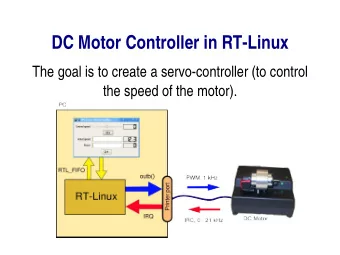

Systems Design and Programming Basic I/O I CMPE 310 Handshaking I/O devices are typically slower than the microprocessor. Handshaking is used to synchronize I/O with the microprocessor. A device indicates that it is ready for a command or data (through some I/O pin or port). The processor issues a command to the device, and the device indicates it is busy (not ready). The I/O device finishes its task and indicates a ready condition, and the cycle continues. There are two basic mechanisms for the processor to service a device. Polling: Processor initiated. Device indicates it is ready by setting some sta- tus bit and the processor periodically checks it. Interrupts: Device initiated. The act of setting a status bit causes an inter- rupt, and the processor calls an ISR to service the device. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Handshaking A printer connected to the parallel port requires handshaking. The parallel port specification is shown below: 13 19 1 25 20 2 DB25 CENT36 Function DB25 CENT36 Function 12 21 24 3 11 1 1 Data Strobe 12 12 Paper out 22 4 23 23 5 10 2 2 Data0 13 13 Select 24 22 6 9 3 3 Data1 14 14 Afd 25 7 21 26 8 8 4 4 Data2 15 32 Error 20 27 9 7 5 5 Data3 16 - RESET 28 10 19 6 29 11 6 6 Data4 17 31 Select in 18 30 12 5 7 7 Data5 18-25 19-30 GND 31 17 13 4 32 8 8 Data6 - 17 Frame GND 14 16 33 15 3 9 9 Data7 - 16 GND 15 34 16 2 35 10 10 Ack - 33 GND 17 14 36 1 18 11 11 Busy DB25 CENT36 The processor writes ASCII data out to the Datax pins of the printer and toggles the Data Strobe pin to latch it in. The printer raises the Busy pin. When the Busy pin goes low, the sequence repeats. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Interfacing Circuitry The terminal characteristics of the processor must be matched to those of the I/O devices. Input Devices: They are either: TTL (0.0V-0.8V low and 2.0-5.0V high) or compatible. Switch-based; usually either open or connected. These must be conditioned before they can be used properly. For example, to make a simple (single-pole, single-throw) toggle switch TTL compatible: The value of R can vary between 1K and 10K Ω . VCC This ensures that the output is held 2.2k Ω at either 0 or logic 1 TTL Output at all times (it never SPST fl oats). L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Interfacing Circuitry Input Devices: Mechanical switches physically bounce when they are closed (causing them to momentarily open after being closed). This can cause a problem if they are used as a clocking signal. Two asynchronous fl ip-fl op solutions ar e given below: VCC A B Q 1k Ω Q 74LS00 D D 74LS04 74LS04 Q Q D D 74LS00 1k Ω More practical inverter implementation. VCC Cross-coupled NANDs. The basic idea is that these fl ip-fl ops stor e the values even if the D/D nodes both fl oat. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 Interfacing Circuitry Output Devices: Interfacing an output device requires matching the voltage and current relationships of the devices and processor. Remember that the standard output levels of TTL compatible devices are 0.0 to 0.4V for logic 0 and 2.4V to 5.0V for logic 1. The current levels are 0.0 to 2.0mA (logic 0) and 0.0 to -400uA (logic 1). For example: Light Emitting Diode 2N2222 has gain of ~100. Requires 10mA of current Base current should be VCC to light. 0.1mA. Assume ~2.0V falls across the With a minimum high of diode and supply is 5V. 2.4V and a 0.7V BE drop, R 1 = 3.0V/10mA = ~300 Ω R 1 330 Ω 1.7V falls across the R 2 . 18K 2N2222 Microprocessor Input R 2 = 1.7V/0.1mA = ~17K. R 2 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O I CMPE 310 I/O Port Decoding For memory-mapped I/O, decoding is identical to memory decoding. For isolated I/O, IORC and IOWC are developed using M/IO and W/R pins of the microprocessor. The text gives examples of 8-bit decoding and 16-bit decoding, which is a straightforward application of devices we’ve used for memory decoding. The I/O banks on the 8086 through the 80386SX are also set up like the mem- ory. BHE BLE (A0) FFFE FFFF FFFC FFFD FFFA FFFB High bank Low bank 0005 0004 0003 0002 0001 0000 D 15 -- D 8 D 7 -- D 0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (April 1, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.