UMBC A B M A L T F O U M B C I M Y O R T 1 - PowerPoint PPT Presentation

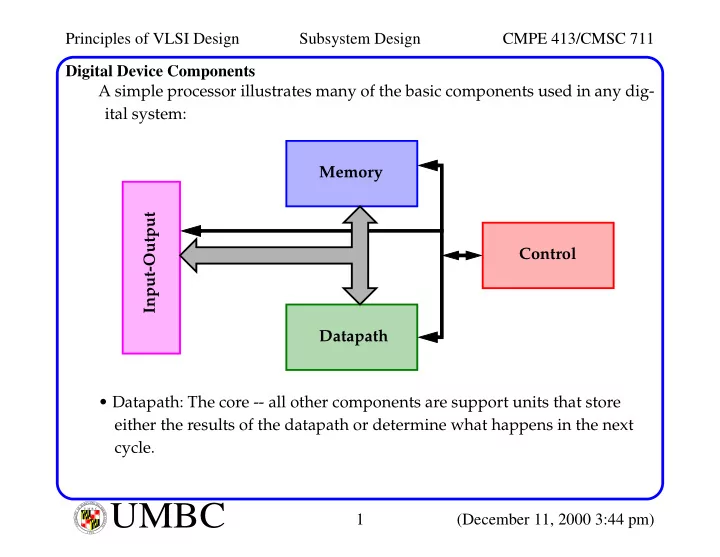

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Digital Device Components A simple processor illustrates many of the basic components used in any dig- ital system: Memory Input-Output Control Datapath Datapath: The core --

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Digital Device Components A simple processor illustrates many of the basic components used in any dig- ital system: Memory Input-Output Control Datapath • Datapath: The core -- all other components are support units that store either the results of the datapath or determine what happens in the next cycle. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Digital Device Components • Memory: A broad range of classes exist determined by the way data is accessed: Read-Only vs. Read-Write Sequential vs. Random access Single-ported vs. Multi-ported access Or by their data retention characteristics: Dynamic vs. Static Stay tuned for a more extensive treatment of memories. • Control: A FSM (sequential circuit) implemented using random logic, PLAs or memories. • Interconnect and Input-Output: Parasitic resistance, capacitance and inductance affects performance of wires both on and off the chip. Growing die size increases the length of the on-chip interconnect, increasing the value of the parasitics. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Digital Device Components Datapath elements include adders, multipliers, shifters, BFUs, etc. The speed of these elements often dominates the overall system perfor- mance so optimization techniques are important. However, as we will see, the task is non-trivial since there are multiple equivalent logic and circuit topologies to choose from, each with adv./ disadv. in terms of speed, power and area. Also, optimizations focused at one design level, e.g., sizing transistors, leads to inferior designs. Bit-sliced organization Control is common for datapaths. Bit 4 Multiplexer Data-Out Registers Data-In Bit 3 Shifter Adder Bit 2 Bit 1 Bit 0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction Let’s start with addition, since it is a very common datapath element and often a speed-limiting element. Optimizations can be applied at the logic or circuit level. Logic-level optimization try to rearrange the Boolean equations to produce a faster or smaller circuit, e.g. carry look-ahead adder. Circuit-level optimizations manipulate transistor sizes and circuit topology to optimize speed. Let’s start with some basic definitions before considering optimizations: A B C i G(A.B) P(A+B) P’(A + B) Sum C o Carry status delete 0 0 0 0 0 0 0 0 delete 0 0 1 0 0 0 1 0 propagate 0 1 0 0 1 1 1 0 0 1 1 propagate 0 1 1 0 1 1 0 0 propagate 0 1 1 1 0 1 0 1 0 1 1 0 1 propagate generate 1 1 0 1 1 0 0 1 1 1 1 1 1 0 1 1 generate L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction G(A.B) : (generate) Occurs when a C o is internally generated within the adder (occurs inde- pendent of C i ). P(A+B) : (propagate) Indicates that C i is propagated (passed) to C o . P’(A XOR B) : (propagate) Used in some adders for the P term since it can be reused to generate the sum term. D(A.B) : (delete) Ensures that a carry bit will be deleted at C o . The Boolean expressions for S and C o are: Sum = A.B.C i + A.B.C i + A.B.C i + A.B.C i = A XOR B XOR C Carry = A.B + A.C i + B.C i L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction But S and C o can be written in terms of G and P’: C o (G, P’) = G + P’C i (or P in this case). S(G, P’) = P’ XOR C i Note that G and P’ are INdependent of C i . (Also, C o and S can be expressed in terms of delete (D)). Ripple-carry adder: A 0 B 0 A 1 B 1 A 2 B 2 A 3 B 3 C i,0 C o,0 C o,1 C o,2 C o,3 FA FA FA FA =C i,1 S 0 S 1 S 2 S 3 The critical path (worst case delay over all possible inputs) is a ripple from lsb to msb . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction The delay in this case is proportional to the number of bits, N, in the input words: t adder = (N - 1)t carry + t sum where t carry and t sum are the propagation delays from C i to C o & S. One possible worst case bit pattern (from lsb to msb ) is: A: 00000001; B: 01111111 Convince yourself that this is true. Note that when optimizing this structure, it is far more important to optimize t carry than t sum . The inverting property of a full adder can be used to achieve this goal: B B A A C i C o C o C i FA FA S S L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction Thus, S(A, B, C i ) = S(A, B, C i ) C o (A, B, C i ) = C o (A, B, C i ) One possible (un-optimized) implementation: A B S Transistor level diagram uses C i 32 transistors. (see Weste and Eshraghian). P’ XOR C i A C i B C o A B G(A.B) C i .P(A + B) L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction C o is reused in the S term as: Sum = A.B.C i + (A + B + C i )C o Symmetrical design A A C i B A A B eliminates diffusion B C i caps and B reduces C o series R. C i C i B S C i A A B A C i A B B Are the n and p trees duals C o 28 transistors of each other? Even with some design tricks, e.g., transistors on the critical path, C i placed closest to the output and symmetrical design, this implementation is slow. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction The load capacitance in previous version on C o consists of 2 diffusion capaci- tances (inverter) and 6 (next bit) gate capacitances: Overflow C<n+1> B<n> C<3> S<n> A<n> B<3> S<3> C<n> A<3> Sign of C<3> the result B<2> B<3> S<2> S<3> A<2> A<3> B<1> B<2> S<1> S<2> A<1> A<2> B<0> B<1> S<0> S<1> A<0> A<1> B<0> Subtract S<0> A<0> Eliminates the inverter delay per bit for carry! C in This version increases C o ’s load to 4 diffusion caps, 2 internal (sum) gate caps plus the 6 (next bit) gate caps. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction Serial addition can be used if area is a concern: Reg 1-bit Clk Set Clr n bit shift register addend C out n bit shift register result augand C in Clk In this case, you want equal Sum and Carry delays in order to minimize clock cycle time. Bit-level pipelining can be used to break the dependency between addition time and the number of bits by inserting FAs between each register bit. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction Transmission-gate Adder: Total transistors is 26 XNOR S B A C o XOR C i Note: S and C o delay times are approximately equal -- good for multipliers. See Weste and Eshraghian for an 18 transistor implementation. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Subsystem Design CMPE 413/CMSC 711 Datapath Operators: Addition/Subtraction Dynamic Adder Design: np-CMOS adder φ φ φ φ S 1 C i1 A 1 B 1 B 1 A 1 A 1 B 1 C i1 A 1 C i B 1 φ φ φ C i2 φ φ φ φ C i1 B 0 C i0 B 0 B 0 C i0 A 0 A 0 A 0 C i0 A 0 B 0 S 0 φ φ φ L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 13 (December 11, 2000 3:44 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.