UMBC A B M A L T F O U M B C I M Y O R T 1 - PowerPoint PPT Presentation

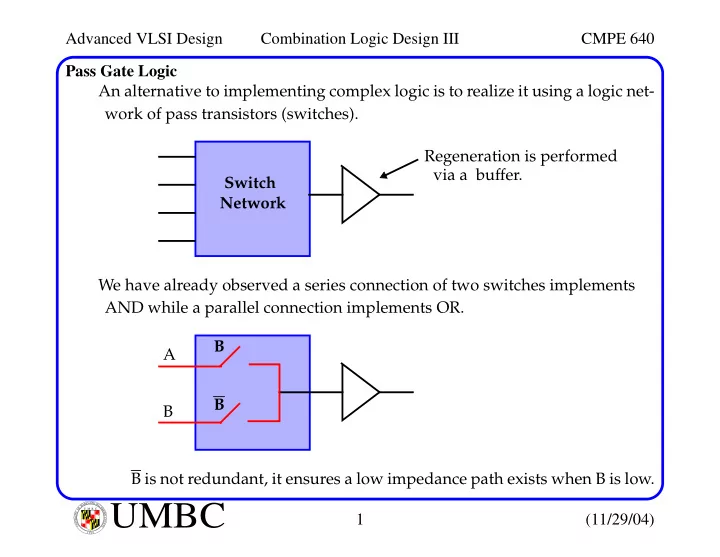

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic An alternative to implementing complex logic is to realize it using a logic net- work of pass transistors (switches). Regeneration is performed via a buffer. Switch

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic An alternative to implementing complex logic is to realize it using a logic net- work of pass transistors (switches). Regeneration is performed via a buffer. Switch Network We have already observed a series connection of two switches implements AND while a parallel connection implements OR. B A B B B is not redundant, it ensures a low impedance path exists when B is low. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Advantage: fast and simple. Complex gates can be implemented using minimum number of transis- tors, which also reduces parasitics. Static and dynamic performance depends on a switch with low parasitic resistance and capacitance. C C A B A B C Transmission gate C Therefore, pass gate networks are often constructed from bi-directional transmission gates. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Both transistors are important: C=5V M 2 A=5V B M n C L M 1 Here, M n turns off when V B reaches (5 - V Tn ) or approximately 3.5V! Note, the V Tn is increased due to the body effect . This reduces the noise margin and increases static power dissipation. Also, the resistance of the switch increases dramatically when the out- put voltage reaches V in -V Tn (linear mode). The combination of both an PMOS and NMOS avoids this problem but requires that the control and its complement be available. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Transmission gates can implement complex gates very efficiently S B B A F = (A*S + B*S) XOR A A S B B B S XOR requires 6 transistors 2-to-1 MUX requires 6 transistors Design Issues: • Resistance. C=0 Parallel connection of resistances R n and R p R n = (V DD - V out )/I n A=5 B R p = (V DD - V out )/I p C L C=5 Currents are dependent on V out and operation region L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Design Issues • Resistance (cont). During the low-to-high transition, the pass transistors pass through sev- eral operation modes. As V GS is always equal to V DS , the NMOS is either in saturation or off. The V GS of the PMOS is V DD , and the device changes from saturation to linear. • V out < |V Tn |: NMOS and PMOS saturated. • |V Tp | < V out < V DD - V Tn : NMOS saturated, PMOS linear. • V DD -V Tn < V out : NMOS cutoff, PMOS linear. It is important to incorporate the body effect when computing I p and I n . The expression for the resistance of a pass gate without the body effect. 1 ≈ R eq - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - ( ) ( ) k n V DD V Tn k p V DD V Tp – + – L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Design Issues • Resistance (cont). Simulated values of : || R eq R p R n = 30 R n 0V 20 R (k Ω) V out 5V R p R eq 10 5V 0 1 2 3 4 5 R eq is relatively constant at 10 k Ω so a constant resistance switch model is reasonable. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Design Issues • Delay 0 0 0 0 V 1 V i-1 V i V i+1 V n-1 V n C C C 5 5 5 5 In order to analyze the response, let’s replace the pass gates with R eq s. R eq R eq R eq R eq V 1 V i-1 V i V i+1 V n-1 V n C C C C C C Delay is found by solving a set of differential equations of the form: ∂ V i 1 ( ) - V i V i 2 V i - - - - - - - - - - - - = + – ∂ t R eq C + 1 – 1 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Design Issues • Delay (cont). An estimate of the dominant time constant at the output of n pass gates: n ( ) n n + 1 ∑ τ V n ( ) CR eq k CR eq - - - - - - - - - - - - - - - - - - - - = = 2 k = 0 Propagation delay is proportional to n 2 ! For large n , it is better to break the chain every m switches and insert buffers: m m R eq R eq V n C C C C C C Total delay assuming buffer delay is t buf is: ( ) ( ) 0.69 n m m n m n n t buf t buf + 1 + 1 t p - CR eq 0.69 CR eq - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - = + - - - - – 1 = + - - - - – 1 m m m 2 2 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Design Issues • Delay (cont). Here, delay exhibits only a linear dependence on the # of switches n . The optimal number of switches, m opt , between buffers is found: ∂ t p t pbuf m opt = 1.7 - - - - - - - - - - - - - = 0 ∂ CR eq m As t buf increases, the number of switches grows. In current technologies, m opt is typically 3 or 4. For example, assume R eq = 10k Ω , C = 10fF, and t pbuf = 500ps. This yields an optimal value of m equal to 3.8 . Therefore, a buffer every 4 transmission gates is suggested. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 Pass Gate Logic Design Issues • Transistor sizing Pass gate logic family is a member of the ratioless logic class. The dc characteristics are not affected by the sizes. Performance, to the first order, is not impacted by changing the W/L. Increasing the size reduces the resistance, but this is offset by the increase in diffusion capacitance. Therefore, minimum sized devices should ALWAYS be used, unless the chain drives a significant external load capacitance. In this case, ordering transistors from largest to smallest in the pass gate chain will help reduce delay. This is analogous to the argument given earlier for logic gate transis- tors close to the output. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 NMOS-Only Transmission Gate Disadvantages of pass gate: • Requires both NMOS and PMOS, in different wells. • Both true and complemented polarities of the control signal needed. • Parallel connection of both transistors increases node capacitance. Therefore, an NMOS-only version is advantageous. Problems: • Reduced noise margins due to the threshold voltage drop. • Static power consumption. C=5V M 2 A=5V B M n C L M 1 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design III CMPE 640 NMOS-Only Transmission Gate One solution is to add a PMOS device, called a level restorer . Level restorer B M r M 4 M 2 5V X A M n M 3 M 1 The output of the inverter is "feedback" as a control signal. It turns on when the inverter output goes low (V out < V DD - |V tp |) and restores node X to V DD . This eliminates the static power consumed. However, the size of the PMOS transistor is important, since a conflict is cre- ated during switching. For example, assume node A =0, storage node X =V DD and B =0->1. A conducting path exists from V DD -M r -M n -M 3 -GND. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (11/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.